### **Semiconductor Device Simulation**

- motivation and target applications

- compact model development under conditions relevant for circuit design

- development of test structures and measurement methods

- (fast) predicting device performance and compact model parameters of next generation Si/SiGe bipolar processes (for process development support)

- most important features of DEVICE

- solves in one-, two-, three-dimensional (rectangular) structures

- Poisson's as well as continuity and transport equations for electrons and holes

- combination of Poisson's and majority continuity equation for fast simulation of electrical coupling between (lossy) device regions at high frequencies (no inductors yet)

- conventional drift-diffusion model

- material parameters: Si, SiGe

- field dependent mobility, high-doping effects, dependence on lattice temperature

- operation modes: DC, transient (time domain), small-signal frequency domain

- circuit simulation capability (using modified nodal analysis)

- numerical device can be embedded in a circuit → mixed-mode device/circuit simulation

- contains compact models such as HICUM and serves as reference simulator for verification of HICUM implementation in commercial circuit simulators

- produces output directly suitable for compact modeling (f<sub>T</sub>, y-parameters, internal model variables)

## Scaling issues (1/4)

- circuit design, especially for high-speed and high-frequency applications, requires optimization via device sizing

- → requires availability of *many* different transistor configurations (E width and length; number of E, B, C fingers)

- → scalable compact models: equations for calculating each equivalent circuit element as a function of device geometry

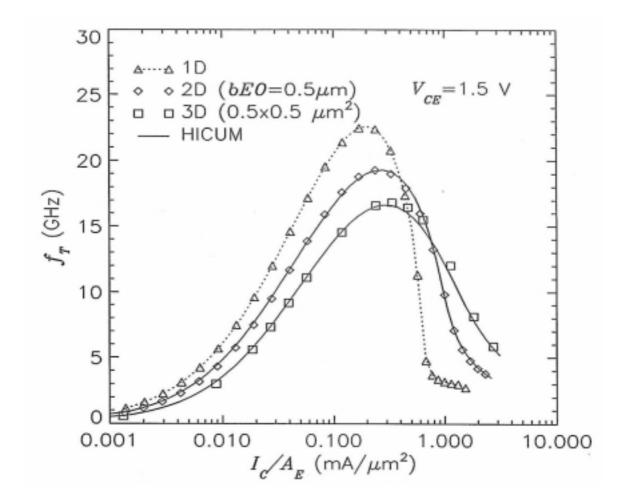

- impact of emitter size on transit frequency:

## Scaling issues (2/4)

- use device simulation to investigate as a function of emitter size and for different processes

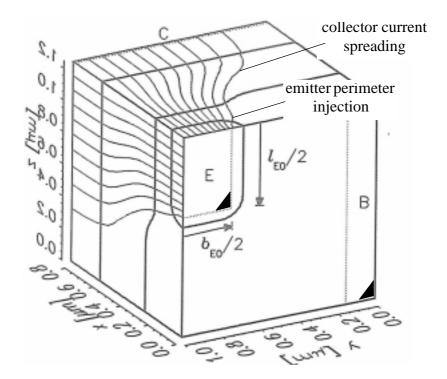

- perimeter injection (current and charge)

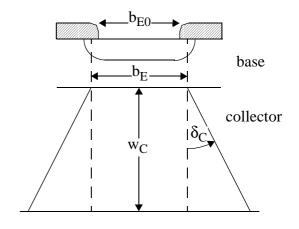

- collector current spreading

- compact model development

- analytical equations for current and charge

- appropriate equivalent circuit representation

collector current spreading at high current densities

## Scaling issues (2/4)

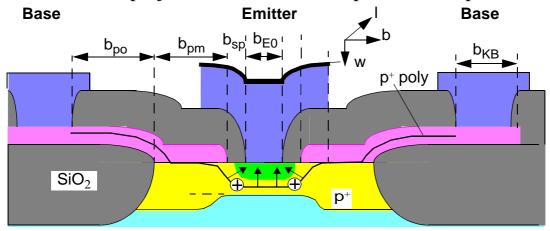

base resistance as a function of "geometry"

- theory exists for

- 2D geometry = long emitter stripe with one or two base contacts in parallel

- circular emitter

- rectangular emitter (approximate solution)

- needed: continuously scalable compact equations for *realistic* transistor geometries used for *integrated* circuit design

- issue: no suitable measurement method for r<sub>B</sub>

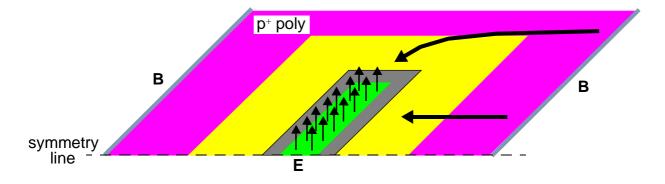

schematic cross-section of relevant transistor region and projection of hole current path into 2D plane

# Scaling issues (2/4)

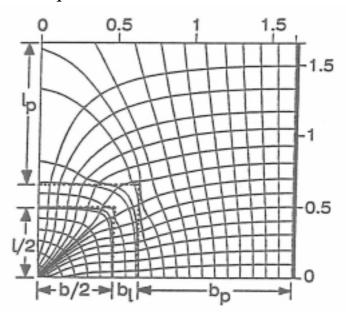

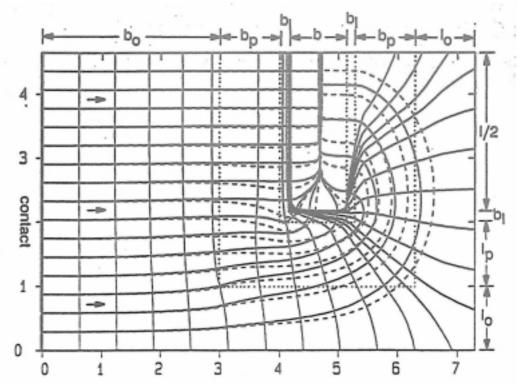

current low lines and equipotential lines

square-emitter structure

single-base rectangular structure with 1:5 aspect ratio

## Mixed-Mode Simulation (1/2)

### High-speed switching

- verification of compact model in realistic circuit environment

- fast switching processes are extremely difficult to measure and require expensive equipment

- simple inverter

- charge storage modeling

- hard-saturation

- ...

- (basic) circuit building blocks

- impact of transistor operation in extreme regimes on circuit behavior

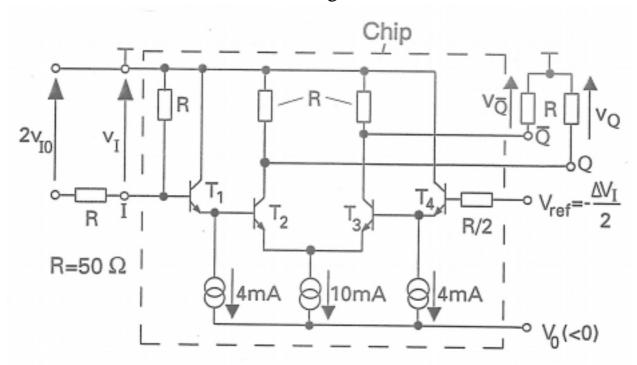

#### ECL gate

## **Mixed-Mode Simulation (2/2)**

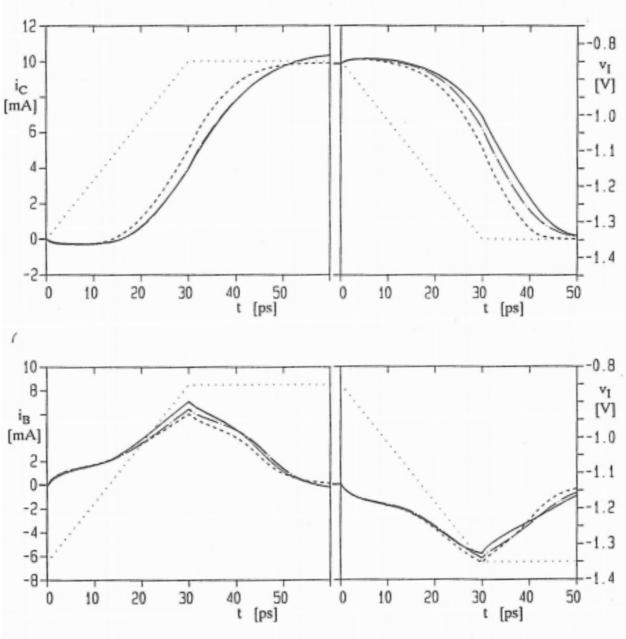

high-speed transients in a current switch: time dependence of collector and base current

comparison: numerical transistor (solid lines), HICUM (dashed lines)

(on-state collector current =  $1 \text{mA/}\mu\text{m}^2$ )