# Accurate transit time determination and transfer current parameter extraction

T. Rosenbaum, A. Pawlak, J. Krause, M. Schröter

**Chair for Electron Devices and Integrated Circuits (CEDIC)**

University of Technology Dresden Germany

Dept. of Electrical and Computer Engin.

University of California at San Diego USA

mschroter@ieee.org, rosenbau@iee.et.tu-dresden.de

http://www.iee.et.tu-dresden.de/iee/eb/eb\_homee.html

12<sup>th</sup> HICUM Workshop Newport Beach (USA), 2012

### **Outline**

- 1 Motivation

- 2 Method overview

- 3 Intrinsic transistor

- 4 Fit procedure

- 5 Results

- 6 Conclusions

#### **Motivation**

- HICUM/L2 is a charge-based model

- physics-based modeling of charge for accurate description of dynamic transistor behavior

- charge components are being used also in transfer current formulation via GICCR

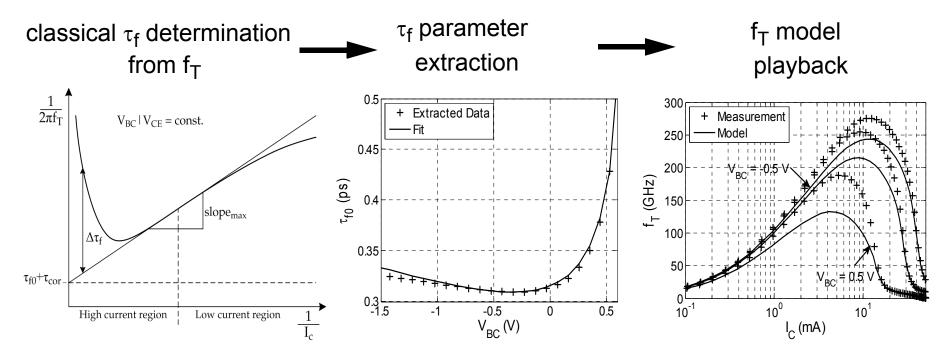

- Observation in more advanced technologies: "classical" determination method of transit time from f<sub>T</sub> measurement appears to be inaccurate or inconsistent

=> inaccurate  $\tau_f$  determination or extraction?

#### **About this presentation ...**

- Goal: develop reliable method for

- transit time determination and model parameter extraction (20 parameters)

- transfer current model parameter extraction (13 parameters)

- Requirements

- accurate and consistent

- include impact of parasitic elements and self-heating

- allows automation (i.e. avoid manual fine tuning)

- applicable to all process technology types

- include new HICUM/L2 v2.31 improvements:

- Barrier term (essential especially for HBTs)

- · Transfer current formulation

- Verification

- IHP HBTs with peak (fT, fmax) = (300, 500) GHz

#### **Method overview**

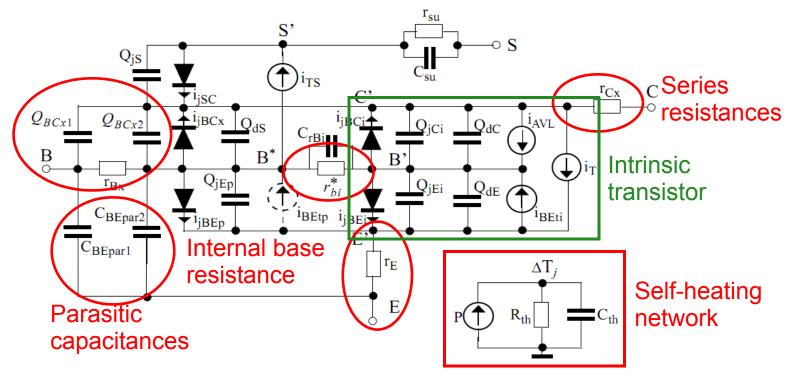

- Transit time is associated with the intrinsic transistor portion

- External elements alter Y-parameters of intrinsic transistor

- in addition: self-heating needs to be included for high current region

## => "De-embedding" of external elements and parasitic effects necessary

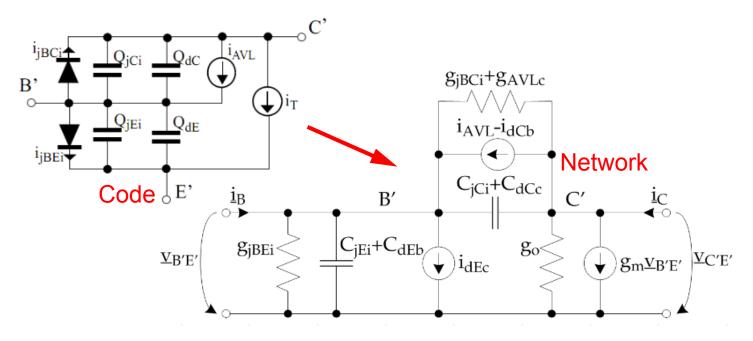

#### **HICUM/L2** equivalent circuit

#### **De-embedding procedure**

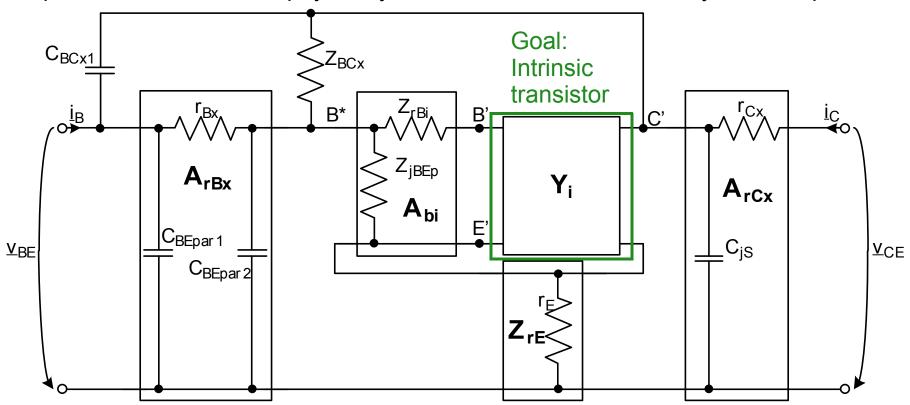

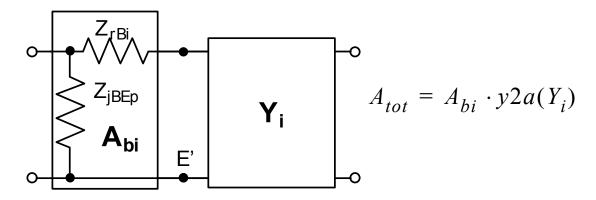

#### Transistor in common-emitter configuration (small-signal EC)

• express each element or physically associated set of elements by sub-two-port

- for sake of simplicity: two-ports of  $C_{BCx1}$  and  $Z_{BCx}$  are not shown in figure

- => various possibilities, above solution is not unique

#### **De-embedding procedure**

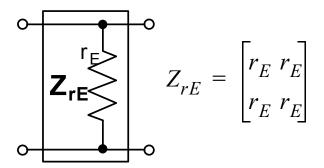

- Calculate two-port parameters of each sub-two-port (example below)

- choose suitable description for easy calculation (e.g. Y, Z or A parameters)

- Determine behaviour of total equivalent circuit by means of two-port analysis

- only simple matrix operations and two-port parameter conversion (e.g. Y → A) are needed

=> perform step by step operations until two-port is fully reproduced

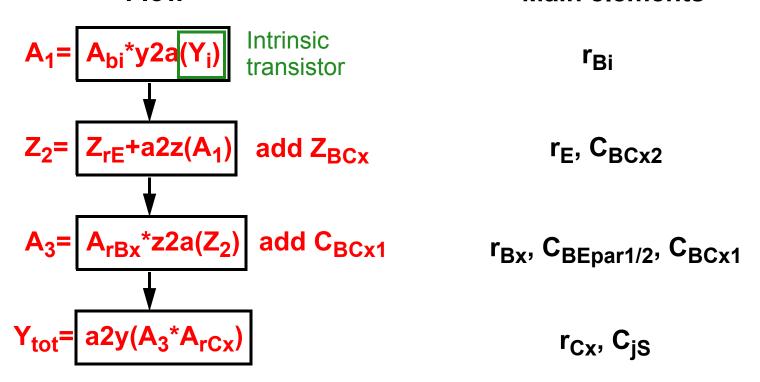

#### **Flowchart**

# ... steps depend on two-port arrangement of equivalent circuit Flow Main elements

- Rearrange equations to calculate Yi

- Y<sub>tot</sub> is known from measurements, parasitic elements are known from beforehand extraction

#### => Intrinsic Y-parameters can be obtained!

#### Intrinsic transistor

• Analysis of the HICUM code shows: complete set of derivatives (small-signal elements) are created due to the implementation in Verilog-A (e.g.  $d(\tau_{f0}) / d(V_{BC}) * I_{Tf}$ )

Transit time is included within the capacitance C<sub>dEb</sub>, combining

$$\Im\{y_{i11} + y_{i21}\}/\omega = C_{dEb} + C_{jEi} = \tau_f \cdot g_m + I_{Tf} \cdot \frac{\partial \tau_{f0}}{\partial V_{B'C}} + C_{jEi}$$

=> sum of  $y_{i11}$  and  $y_{i21}$  includes  $\tau_f$  as well as other elements

#### Fit procedure

re-arrange equation for fit

$$\tau_{fit} = \frac{\Im\{y_{i11} + y_{i21}\}}{g_m \omega} = \tau_f + \frac{C_{\tau f0} + C_{jEi}}{g_m}$$

with

$$C_{\tau f0} = I_{Tf} \cdot \frac{\partial \tau_{f0}}{\partial V_{B'C'}}$$

and  $g_m \approx Re\{y_{i12} + y_{i21}\}$

equation contains 21 parameters in total

#### => Least square fit is likely to fail

- Split transit time by separating the low- and high-current transit time portion

- · depletion capacitance dominates at low bias

- high-current transit time portion  $\Delta \tau_f$  dominates at high bias

=> apply fit to smaller subsets

=> coupling of subsets is required for final solution

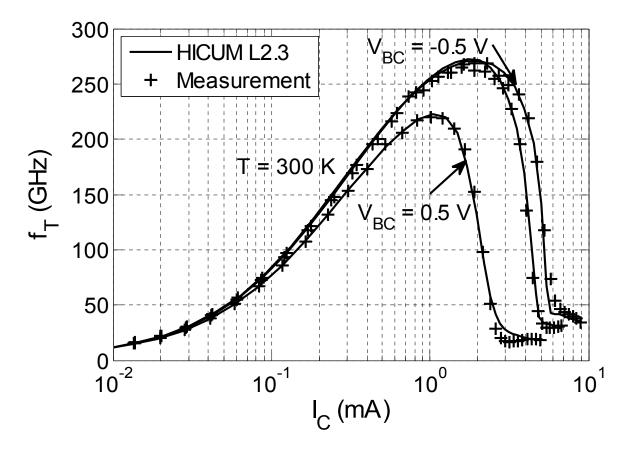

#### **Results**

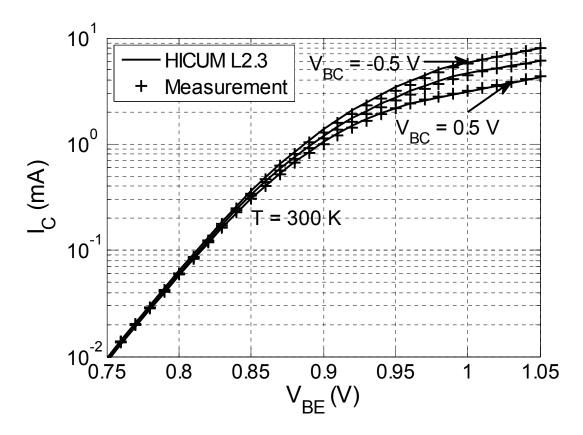

• Transit frequency (SiGe HBT from 130nm IHP process technology)

- New extraction method can provide accuracy similar to a manual procedure

- · High current characteristics is usually even more accurate as self heating is included

# Transfer current of high-speed HBT (SiGe HBT from 130nm IHP process technology)

Results are similar to a procedure with time consuming manual fine tuning

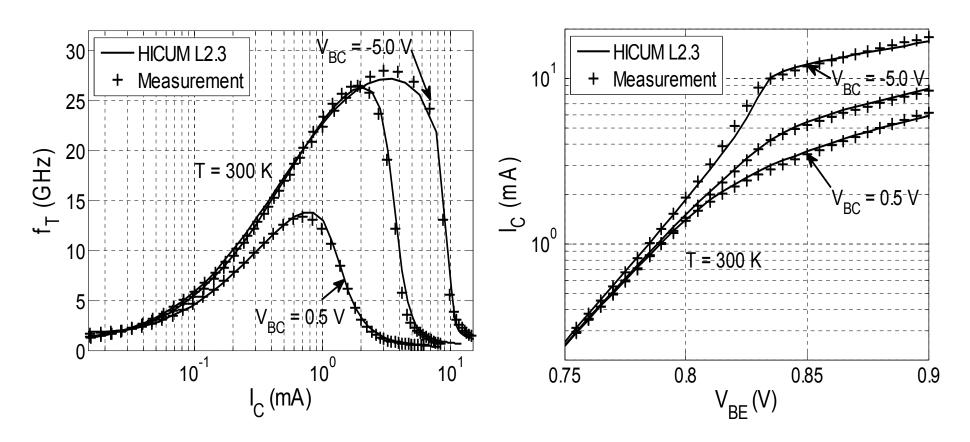

#### **High-voltage SiGe HBT (IHP)**

#### **Transit frequency**

#### transfer current

=> Extraction also suitable for HV-transistors

#### **Conclusions**

- observed discrepancy between measured and modeled transit frequency is due to inconsistent transit time determination from measurements in standard method =>  $\tau_f$  cannot be accessed directly using  $f_T$

- problem can be fixed by careful "de-embedding" of intrinsic transistor Y parameters

- method was shown to be consistent and very accurate

- with extraction fully adapted to HICUM/L2 v2.31

- method was implemented in automated extraction tool

- adaption to model changes is easy (exchange of equations or transfer function only)

- still: lot of settings are required to conduct the extraction

#### Issues

- accuracy depends on accuracy of information on several parasitic elements especially: handling of internal base resistance is difficult

inaccurate settings might render final results useless

- implementation needs to be changed with each model (eq. or equivalent circuit) change

- method is generally useful for extractions from device simulation and model development