Departement Elektriese, Elektroniese & Rekenaar-Ingenieurswese Department of Electrical, Electronic & Computer Engineering Kgoro ya Merero ya Mohlagase, Elektroniki & Bointšinere bja Khomphutha

### Research framework

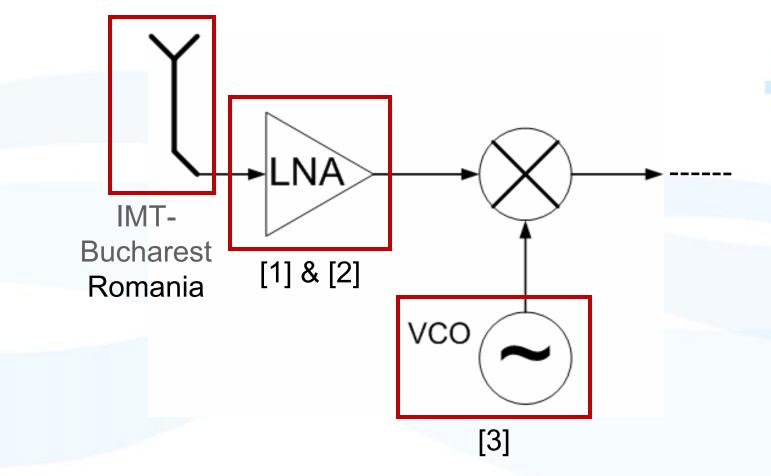

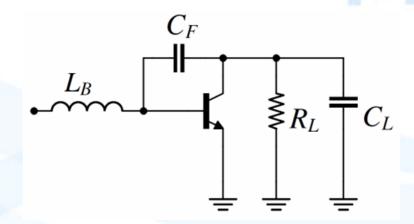

# Previous narrowband 60 GHz LNA attempt

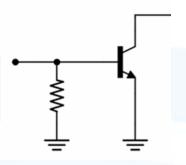

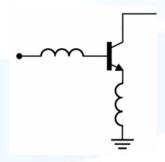

- Inductive emitter degeneration input matching

- 22 dB Gain (3 stages)

- 100 mW power consumption

- Limited simulation due to HIT-kit incompatibility with Mentor Graphics IC flow

- No DRC was possible

### Real-world applications

#### 60 GHz LNA:

- High data rate short range wireless networks

- 'Cable free' home theatre systems

#### **UWB & Ku-band LNAs:**

- Software radio type applications

- •1-18 GHz receiver with 800 MHz bands

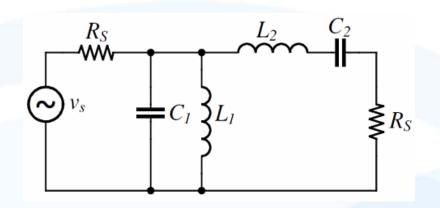

## Ku-band SiGe BiCMOS

**LNA**

| Bandwidth        | 1 – 18 GHz |  |

|------------------|------------|--|

| Gain             | 18 – 22 dB |  |

| NF               | < 4 dB     |  |

| P <sub>1dB</sub> | -10 dBm    |  |

| Parameter    | IBM 8HP | IBM 7WL |

|--------------|---------|---------|

| β            | 600     | 140     |

| $f_T$ (peak) | 200 GHz | 60 GHz  |

| $r_b$        | 20 Ω    | 20 Ω    |

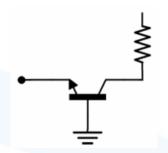

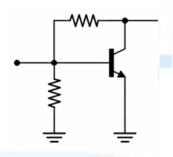

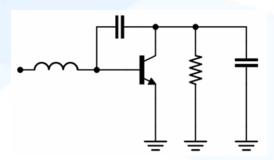

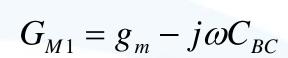

## **Current matching techniques**

Resistive termination

$1/g_m$  termination

Resistive shunt-shunt feedback

Inductive degeneration Capacitive shunt-shunt feedback

LC-ladder and inductive degeneration

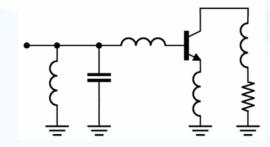

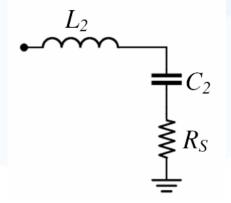

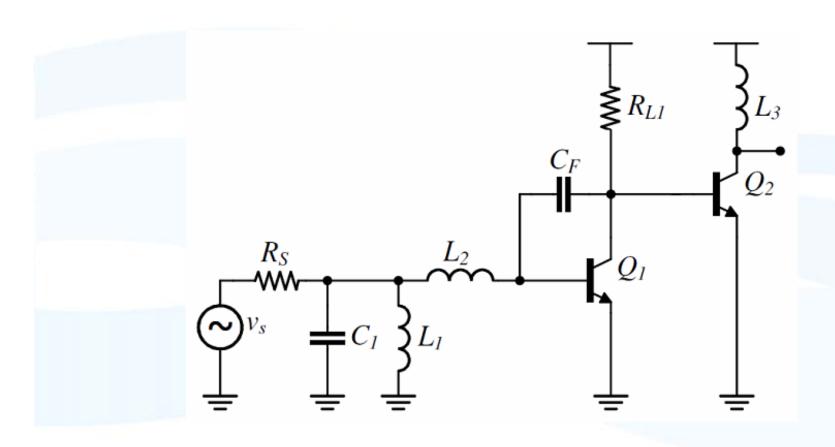

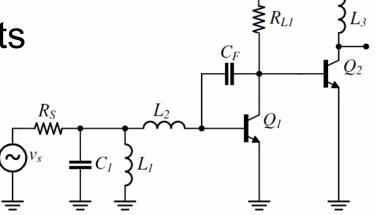

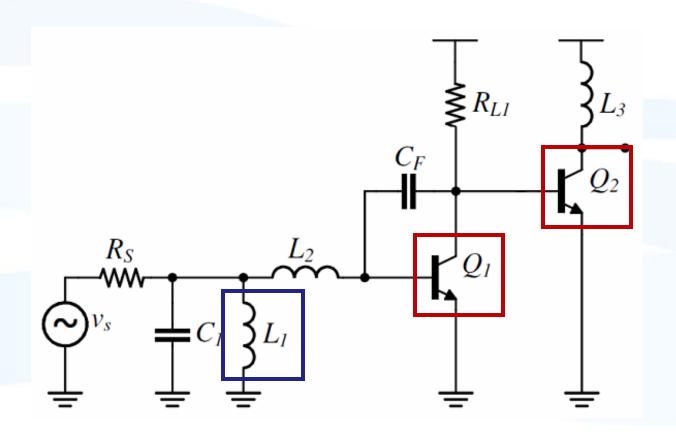

# LC-ladder & capacitive feedback configuration

$$Z_{M} = \frac{1}{j\omega C_{F}(1+g_{m}R_{L})} + \underbrace{\frac{R_{L}}{1+g_{m}R_{L}}\left(1+\frac{C_{L}}{C_{F}}\right)}_{R_{M}} = \underbrace{\frac{1}{j\omega C_{F}(1+g_{m}R_{L})} + \underbrace{\frac{R_{L}}{1+g_{m}R_{L}}\left(1+\frac{C_{L}}{C_{F}}\right)}_{R_{M}}}_{= \frac{1}{2}}$$

$$C_2 = C_{\pi} + C_M \qquad R_S = R_M \left( \frac{C_M}{C_M + C_{\pi}} \right)^2$$

### Gain

Stage

$$Z_{L1} = R_L \left\| \frac{1}{j\omega(C_{BC} + C_L)} = \frac{R_L}{1 + j\omega R_L(C_{BC} + C_L)} \right\|$$

Stage

$$A_{v,2} = j\omega L_3 g_{m2}$$

2:

## **Proposed LNA schematic**

## **Design equations**

$$L_1 \approx \frac{R_S}{\omega_L}$$

$C_2 \approx \frac{1}{\omega_L R_S}$

$L_2 \approx \frac{R_S}{\omega_U}$   $C_1 \approx \frac{1}{\omega_U R_S}$

$$C_2 = C_{\pi} + (1 + g_m R_L)(C_{\mu} + C_F) \implies C_F = \frac{C_2 - C_{\pi 1}}{1 + A_{\nu 1}} - C_{\mu 1}$$

$$R_S \approx \frac{1}{g_m} \left( 1 + \frac{C_L}{C_{BC}} \right)$$

$\Rightarrow I_C \approx \left( 1 + \frac{C_L}{C_{BC}} \right) \frac{V_T}{R_S}$

$$[g_m R_L >> 1 \text{ and } C_M >> C_\pi]$$

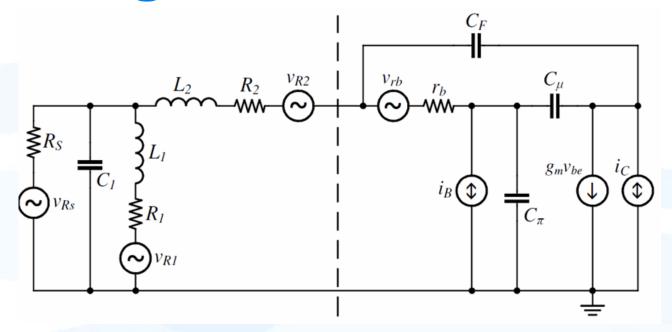

## Noise figure

$$F_{1} = \frac{\overline{v_{\pi,veq}^{2} + \overline{v_{\pi,ieq}^{2} + \overline{v_{\pi,R1}^{2} + \overline{v_{\pi,R2}^{2} + \overline{v_{\pi,RS}^{2}}}}}{\overline{v_{\pi,RS}^{2}}}$$

$$= \left[ \left( \frac{1}{\left| Z_{S} \right|^{2}} + \left| 1 + \frac{Z_{2}}{Z_{S}} \right|^{2} \cdot \left| \omega C_{F} \right|^{2} \right) \overline{v_{CE}^{2}} + \left| 1 + \frac{Z_{2}}{Z_{S}} \right|^{2} \overline{i_{CE}^{2}} + \frac{1}{\left| Z_{1} \right|^{2}} \overline{v_{R1}^{2}} + \frac{1}{\left| Z_{S} \right|^{2}} \overline{v_{R2}^{2}} + \frac{1}{R_{S}^{2}} \overline{v_{RS}^{2}} \right] \cdot \frac{R_{S}^{2}}{\overline{v_{RS}^{2}}}$$

### Noise contributions vs.

frequency nest Equivalent noise voltage [V²/Hz]  $n_{RL2}$  $n_{A2}$ 10 18 Frequency [GHz]

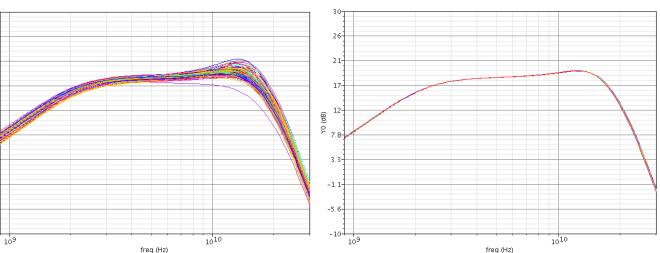

## S<sub>11</sub> and gain results

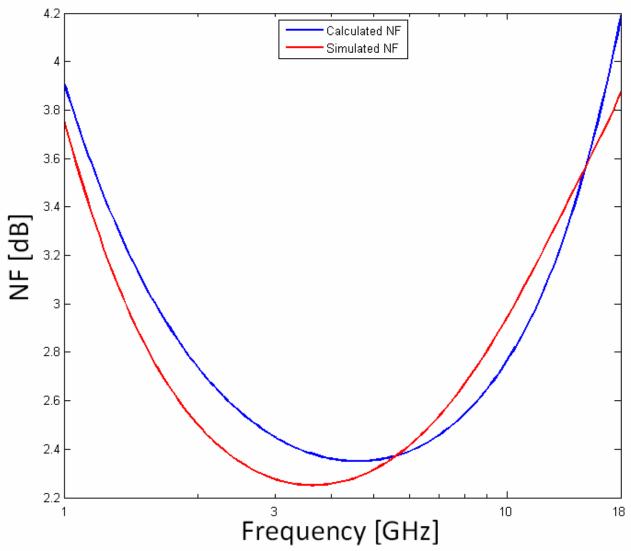

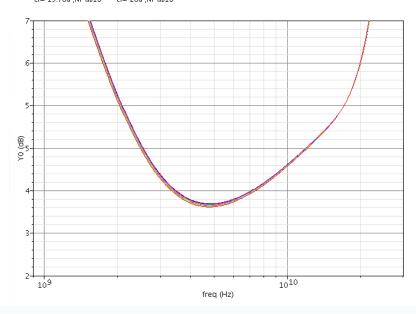

## Noise figure results

## Design at 60 GHz

#### **Design limitations:**

- Input impedance approximation

- Transistor gain-bandwidth product

On-chip passive components

#### Performance tradeoffs:

- NF vs. Bandwidth

- Parasitic capacitance vs.

$\omega_L$

# Monte Carlo Analysis Dominant Sensitive Components

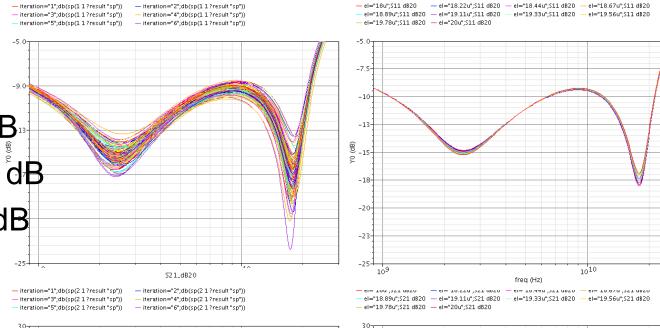

## **Monte Carlo Analysis –** S<sub>11</sub> &

S<sub>21</sub>

$\Delta S_{11@3GHz} \approx 3 \text{ dB}$   $\Delta S_{11@3GHz} \approx 1.8 \text{ dB}$   $\Delta S_{11@18GHz} \approx 7 \text{ dB}$

$\Delta S_{21} \approx 1.2 \text{ dB}$  $\Delta S_{21peak} \approx 3 \text{ dB}$

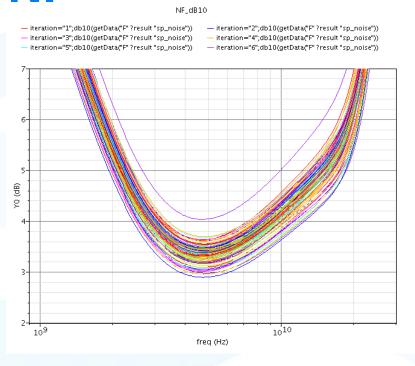

# **Monte Carlo Analysis – NF**

#### Expressions 3

el="18u";NF dB10

el="18.22u";NF dB10

el="18.44u";NF dB10

el="18.64u";NF dB10

el="19.13u";NF dB10

el="19.33u";NF dB10

el="19.56u";NF dB10

el="19.78u";NF dB10

ΔNF ≈ 1 dB

#### **Future work**

During internship at TU-Dresden:

Simulate using HICUM models and compare with well documented theoretical and simulation results thus far.

#### References

- [1] M. Weststrate and S. Sinha, "Analysis of a Low Noise Amplifier with LC-Ladder Matching and Capacitive Shunt-Shunt Feedback," *Proc. IEEE Africon* 2009, Nairobi, 23-25 September 2009.

- [2] C. Janse van Rensburg, "SiGe BiCMOS LNA for mm-wave applications", Master's degree dissertation, Dept.: Electrical, Electronic & Computer Eng., Nov. 2010, University of Pretoria, South Africa.

- [3] D. George, "SiGe based multiple-phase VCO operating for mm-wave frequencies", PhD thesis, Dept.: Electrical, Electronic & Computer Eng., Nov. 2010, University of Pretoria, South Africa.

- [4] A. H. Uys, "Design of a SiGe based 60 GHz low noise amplifier," BEng (Electronic Engineering) final year project report, Dept.: Electrical, Electronic & Computer Eng., November 2008, University of Pretoria, South Africa.

- [5] M. Weststrate and S. Sinha, "Mathematical Analysis of Input Matching Techniques for Application in Wide-band LNA Design," *Proc. of the South African Conference on Semi- and Superconductor Technology*, Stellenbosch, 8-9 April 2009, pp. 128 132.

- [6] M. Weststrate and S. Sinha, "Noise optimization of a wideband capacitive shunt-shunt feedback LNA design suitable for software-defined radio," Accepted for publication in the *Proc. of the IEEE International Conference on Electronics, Circuits and Systems* 2009, Hammamet, 13-16 December 2009.

- Capacitive Feedback LNA and Scaling to mm-Wave Frequencies," Proc. IEEE

#### Feedback/Questions

#### **Marnus Weststrate**

Carl & Emily Fuchs Institute for Microelectronics

Dept.: Electrical, Electronic & Computer Engineering

University of Pretoria

Pretoria 0002

SOUTH AFRICA

E-mail: MarnusW@ieee.org

#### Acknowledgements

2. The authors would like to thank the Federal Ministry for Education and Research (BMBF), **IRF** Germany and National Research Foundation (NRF), South Africa for sponsoring travel, subsistence and related costs towards "exchange" stay in Germany.

Federal Ministry