Physics- and process-based bipolar transistor modeling for integrated circuit design

## **Motivation**

- Increasing demand on circuit performance  $\rightarrow$  often requires transistor operation close to the process performance limit  $\Rightarrow$  design measures:

- careful circuit optimization through proper transistor sizing

- process variations need to be included

- Large variety of circuit applications → overall required number of transistor configurations<sup>1</sup> can become very large (>100) ⇒ need geometry scalable compact models

- Reduce time-to-market: start circuit design during process development (*concurrent engineering*)

⇒ predicted but consistent model parameters and flexible parameter generation

- Align process development with product (design) needs

- ⇒ quick evaluation of process change impact on electrical device and circuit performance

- Include process tolerances in design:

- statistical modeling

- matching

<sup>1.</sup> defined by emitter dimensions  $b_{E0}$  and  $l_{E0}$  ( $\ge b_{E0}$ ), number of emitter, base, and collector fingers/contacts and their spatial arrangement

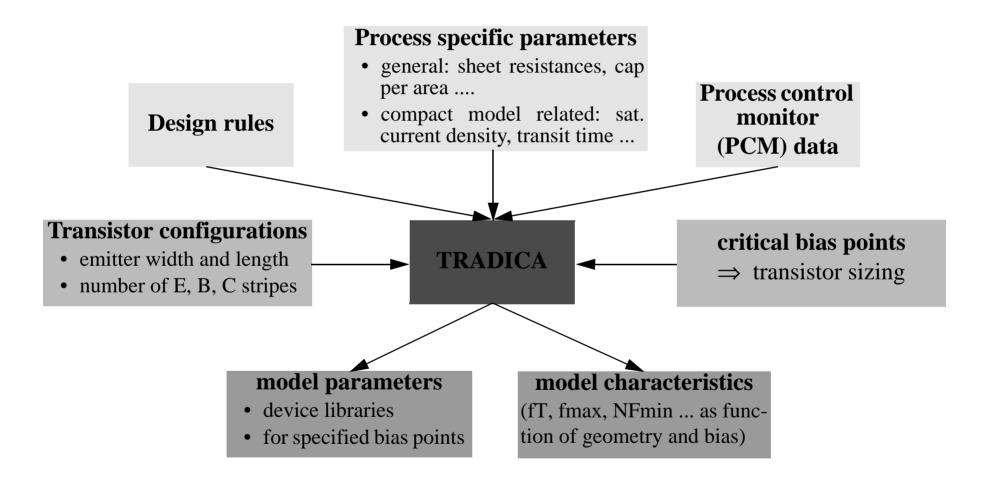

#### **TRADICA overview**

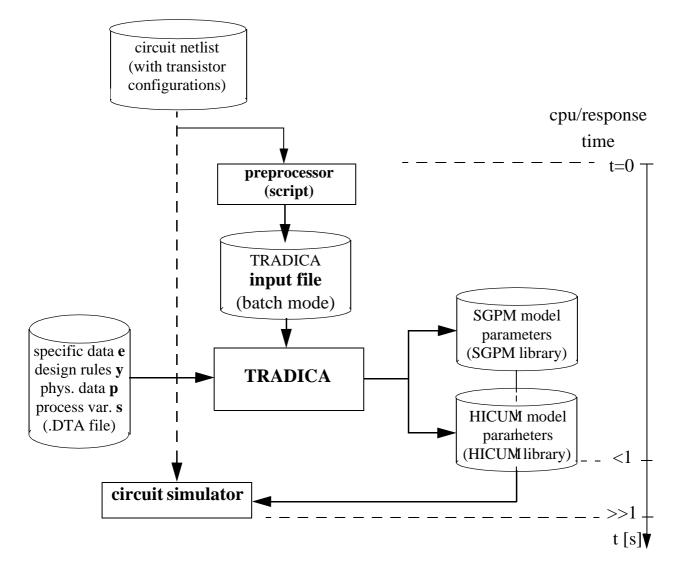

## Integration of TRADICA in RF design system

- Benefits:

- circuit optimization via consistently scalable transistor models

- statistical and matching simulation

- parameter transfer via single "technology" file (xxxx.DTA)

- ⇒ significant enhancement of functionality for design at reduced maintenance effort for foundry

- Integration scheme:

### **Program features**

- Generation of consistent sets of geometry scalable compact model parameters for

- HICUM

- SGPM

for each: hierarchy of equivalent circuits with different complexity

- Statistical modeling capability

- generation of skewed model parameter sets

- determination of corner-case parameter sets

- Transistor sizing

- Automatic extraction of specific SGPM parameters from specific HICUM parameters

- General features:

- user friendly interactive operation

- batch operation (for integration in extraction and design systems)

- Manual and installation guide available

- platforms: UNIX, Windows

# **Distribution list**

```

Agere

```

Alcatel

Alpha (formerly Conexant's III-V division)

**Atmel**

**Conexant**

**Cypress**

**IBM**

IIT

**Infineon**

Jazz

Maxim

**SiliconWave**

**STMicroelectronics**