# Experiences with Aging Simulation

Christian Maier, Robert Bosch GmbH

# Experiences with Aging Simulation

## Motivation

- ▶ Devices in state-of-the-art semiconductor processes can be operated in regions where degradation may happen

- ▶ Aging simulation needed to take the effect of device degradation during design into account

- ▶ Aging models needed for relevant degradation mechanisms

- ▶ At Bosch, process design kits (PDKs) from different vendors are used

- ▶ Aging simulation not supported in every PDK

# Experiences with Aging Simulation History

- ▶ Main Activities of Bosch regarding reliability simulation within funded projects:

- ▶ Project ELIAS (2007..2010): RelXpert URI improved for support of subcircuit device models (Cadence has been project partner) ➔ Implementation into Cadence 5.1.41

- ▶ Project RESIST (2014...2017): Improvement of reliability simulation flow to support (i.e. enhance) process design kits from different vendors

# Experiences with Aging Simulation

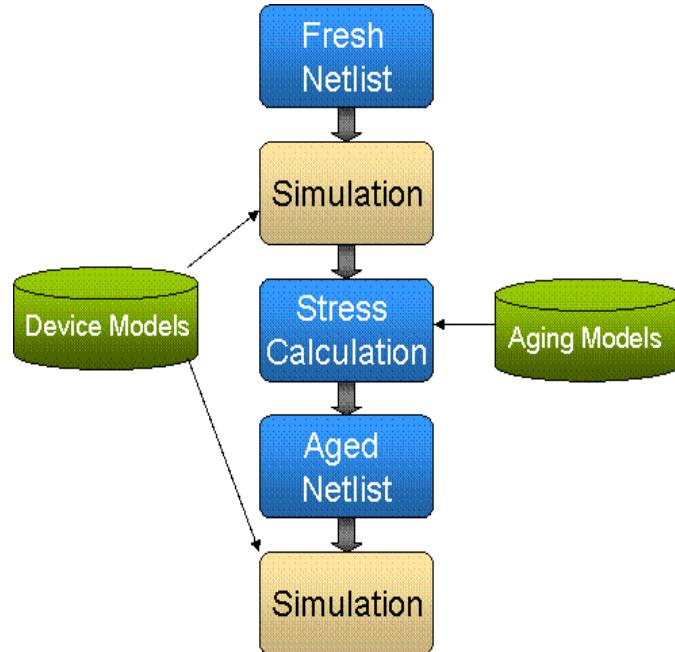

## Aging Simulation Flow with RelXpert

- ▶ Flow is based on BERT methodology (Berkeley Reliability Tools, 1990)

- ▶ Stress is calculated for each device from a transient simulation by use of (built-in or user defined) models describing aging as function of operating point, temperature and time

- ▶ From extrapolation to a specified lifetime, degraded model parameters are calculated and an aged netlist is generated

- ▶ With this netlist, simulation of the “aged” circuit can be performed

- ▶ RelXpert is implemented in Cadence ADE and ADE-(G)XL

# Experiences with Aging Simulation

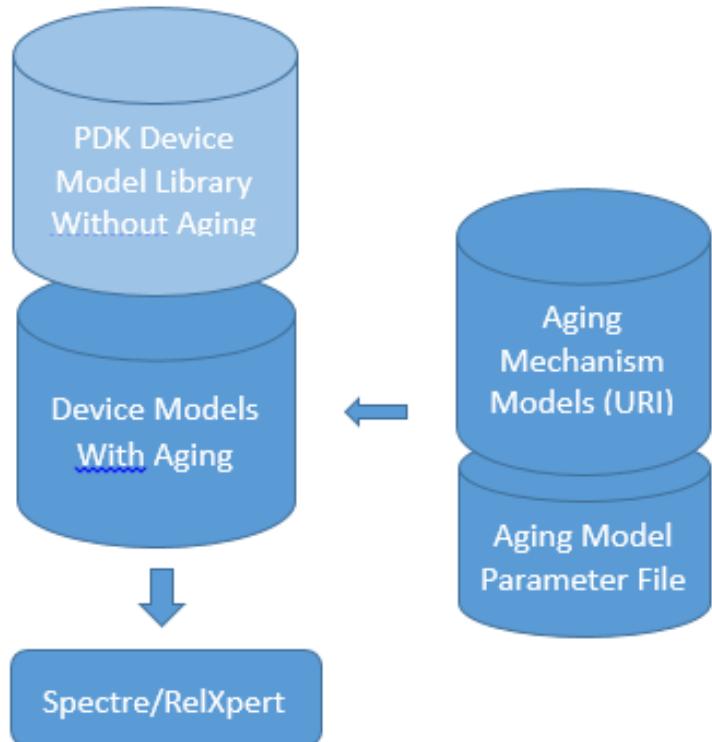

## Modular Approach for Aging Model Implementation

- ▶ Direct modifications in PDKs should be avoided (danger of inconsistency if PDK is updated)

- ▶ Models for aging mechanisms to be added optional as external modules

- ▶ Modules should be applicable to different PDKs of different vendors (→ aging model library process independent)

- ▶ Parameterization of the models at vendor data

# Experiences with Aging Simulation Status

- ▶ Aging models available for CMOS/HVMOS; PBTI, NBTI, HCI

- ▶ Aging simulation could explain observed spec violations, especially regarding mismatch

- ▶ Accepted by designers and integrated in design flow (ADE-(G)XL), if supported by PDK vendor

- ▶ Obstacles

- ▶ Aging data acquisition

- ▶ Accuracy (e.g. recovery effects not modelled, incomplete consideration of mission profile)

- ▶ Software Issues

- Incompatibility (version change)

- Implementation bugs

- Incomplete documentation