# HICUM / L2

# A geometry scalable physics-based compact bipolar

# transistor model

M. Schroter, A. Pawlak, A. Mukherjee

Documentation of model version 2.33

March, 2015

# List of often used symbols and abbreviations

$A_{E0}$ ,  $L_{E0}$  emitter window area and perimeter

A<sub>E</sub>, L<sub>E</sub> effective (electrical) emitter area and perimeter

$b_{E0}$ ,  $l_{E0}$  emitter window width and length

$b_E$ ,  $l_E$  effective (electrical) emitter width and length

I<sub>T</sub>, i<sub>T</sub> DC and time dependent transfer current of the vertical npn transistor structure

I<sub>CK</sub> critical current (indicating onset of high-current effects)

$\mu_n$ ,  $\mu_p$  electron (hole) mobility

N<sub>Ci</sub> (average) collector doping under emitter

N<sub>Cx</sub> collector doping under external base

Q<sub>p</sub> hole charge

$\tau_{\rm f}$  forward transit time

w<sub>B</sub> ,w<sub>B0</sub> neutral/metallurgical base width

w<sub>Ci</sub> (effective) collector width under emitter

w<sub>Cx</sub> (effective) collector width under external base

w<sub>i</sub> width of collector injection zone (for charge storage calculation in collector region)

GICCR Generalized Integral Charge-Control Relation

SGPM SPICE Gummel-Poon model

| I Introduction                                                             | 5  |

|----------------------------------------------------------------------------|----|

| 2 Model equations                                                          | 7  |

| 2.1 Equivalent circuit                                                     | 7  |

| 2.2 Quasi-static transfer current                                          | 9  |

| 2.3 Minority charge, transit times, and diffusion capacitances             | 17 |

| 2.3.1 Minority charge component controlled by the forward transfer current | 17 |

| 2.3.2 Minority charge component controlled by the inverse transfer current | 30 |

| 2.4 Depletion charges and capacitances                                     | 31 |

| 2.4.1 Base-emitter junction                                                | 31 |

| 2.4.2 Internal base-collector junction                                     | 34 |

| 2.4.3 External base-collector junction                                     | 38 |

| 2.4.4 Collector-substrate junction                                         | 40 |

| 2.5 Static base current components                                         | 41 |

| 2.6 Internal base resistance                                               | 44 |

| 2.7 External (parasitic) bias independent capacitances                     | 49 |

| 2.8 External series resistances                                            | 53 |

| 2.8.1 External base resistance                                             | 53 |

| 2.8.2 External collector resistance                                        | 54 |

| 2.8.3 Emitter resistance                                                   | 55 |

| 2.9 Non-quasi-static effects                                               | 56 |

| 2.9.1 Vertical NQS effects                                                 | 56 |

| 2.9.2 Lateral NQS effect                                                   | 57 |

| 2.10 Breakdown                                                             | 59 |

| 2.10.1 Collector-Base Breakdown                                            | 59 |

| 2.10.2 Emitter-base breakdown                                              | 61 |

| 2.11 Substrate network                                                     | 64 |

| 2.12 Parasitic substrate transistor                                        | 66 |

| 2.13 Noise model                                                           | 68 |

| 2.13.1 Thermal and shot noise                                              | 69 |

| 2.13.2 Flicker noise                                                       | 69 |

| 2.13.3 Correlation between base and collector noise                        | 70 |

| 2.14 Temperature dependence                                                | 71 |

| 2.14.1 Temperature dependent bandgap voltage                               | 71 |

| 2.14.2 Transfer current                                                    | 74 |

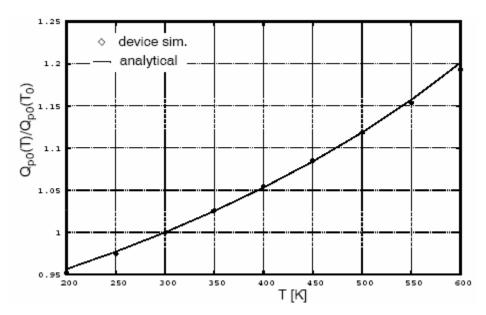

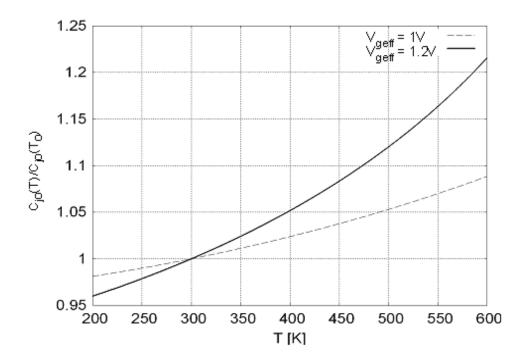

| 2.14.3 Zero-bias hole charge                                               | 75 |

| 2.14.4 Weight factors                                                      | 76 |

| 2.14.5 Base (junction) current components                                  | 77 |

| 2.14.6 Transit time and minority charge                                    | 80 |

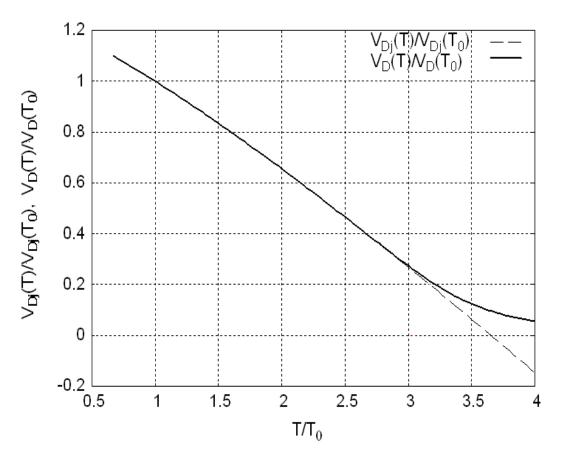

| 2.14.7 Temperature dependence of built-in voltages                         | 82 |

| 2.14.8 Depletion charges and capacitances                                  | 85 |

| 2.14.9 Series resistances                                                  | 86 |

| 2.14.10 Breakdown                                                          | 88 |

| 2.14.11 Base-collector junction (avalanche effect)                         | 88 |

| 2.14.12 Base-emitter junction (tunnelling effect)                          | 88 |

| 2.14.13 Parasitic substrate transistor                                     | 90 |

| 2.14.14 Thermal resistance                                | 90  |

|-----------------------------------------------------------|-----|

| 2.15 Self-heating                                         | 91  |

| 2.16 Lateral scaling                                      | 92  |

| 2.16.1 Bias dependent collector current spreading         | 92  |

| 2.16.2 Emitter current crowding                           | 96  |

| 3 Parameters                                              | 98  |

| 3.1 Transfer current                                      | 99  |

| 3.2 Base-emitter current components                       | 100 |

| 3.3 Base-collector current components                     | 100 |

| 3.4 Base-emitter tunnelling current                       | 101 |

| 3.5 Base-collector avalanche current                      | 101 |

| 3.6 Series resistances                                    | 101 |

| 3.7 Substrate transistor                                  | 102 |

| 3.8 Intra-device substrate coupling                       | 102 |

| 3.9 Depletion charge and capacitance components           | 102 |

| 3.10 Minority charge storage effects                      | 103 |

| 3.11 Parasitic isolation capacitances                     | 104 |

| 3.12 Vertical non-quasi-static effects                    | 105 |

| 3.13 Noise                                                | 105 |

| 3.14 Lateral geometry scaling (at high current densities) | 106 |

| 3.15 Temperature dependence                               | 106 |

| 3.16 Self-Heating                                         | 108 |

| 3.16.1 Circuit simulator specific parameters              | 109 |

| 4 Operating Point Information from Circuit Simulators     | 110 |

HICUM Introduction

#### 1 Introduction

A compact model represents the link between process technology and circuit design. The HIgh-CUrrent Model (HICUM) Level2 (L2) has been a standard compact model for bipolar junction transistors (BJTs) and heterojunction bipolar transistors (HBTs) for many years. The model has been shown to be applicable to SiGe HBTs [27] and also to InP HBTs [33, 34]. This manual documents its latest release and includes the contents of change or release notes up to the version specified on the title page.

The physical background of HICUM/L2 and the derivation of its equations up to version 2.30 have been described in detail in [27], while the extensions beyond v2.30 are described in [28, 29]. Therefore, this manual presents just the (bias and temperature dependent) equations that have been implemented into the latest release of the Verilog-A (VA) model code\* without going into the details of their derivation or assumptions. The model equations are discussed on the basis of a vertical npn transistor. A vertical pnp transistor requires for most processes the addition of a parasitic n-well transistor (e.g. in a subcircuit). Since HICUM has been developed for high-speed applications, in the public domain version described in this document only minimal effort has been undertaken to *very* accurately describe the inverse (or reverse) operating region defined by  $V_{CE}$ <0. The model formulations are extended in a simple way into that bias region in order to mainly ensure numerical stability.

HICUM/L2 is a physics-based compact transistor model in which the value of each element in the equivalent circuit is a function of so-called specific electrical data (such as sheet resistances and capacitances per area or length), technological data (such as width and doping of the collector region underneath the emitter), physical data (like mobilities), transistor dimensions (such as design rules), operating point, and temperature. As a consequence, for arbitrary transistor configurations, defined by emitter size as well as number and location of base, emitter and collector contacts, a complete set of model parameters can be calculated from a single set of technology specific electrical and technological data (cf. [20, 27]). This feature enables circuit optimization as well as statistical modelling and circuit design. In combination with device simulation, even the physical limits of SiGe HBT technology [30, 31] and its technology roadmap can be predicting using the model [32]. Note that geometry scaling equations are not part of this manual since they need to be

© M. Schroter 10/8/15

<sup>\*.</sup>In the following text the actually implemented model equations are marked by a frame.

HICUM

implemented in a preprocessor in order to be sufficiently accurate and flexible for a large variety of transistor configurations and process technologies.

Parameter extraction as well as generation of model parameters for different transistor configurations are not part of this manual since they depend on user preferences. There are two alternatives for parameter extraction. Users may build their own parameter extraction infrastructure by implementing methods gathered from literature. Publications related to extracting HICUM/L2 parameters are, e.g., [35-41]. The other option is to acquire a commercial parameter extraction tool or even use an external service [42].

The history of HICUM/L2 is described in [27]. Its development has so far continued for 30 years. Over its long period of existence, HICUM has been verified for a large variety of bipolar technologies and circuit. For comparisons of the model with experimental results and applications to (production) circuit design, the reader is referred to the literature (e.g. in [27] and more recent journals [43]). Considering the present direction of SiGe and InP HBT technology towards mm-wave and THz applications as well as the involvement of the HICUM/L2 team in the corresponding major flagship projects, it is expected that the model development will continue for a significant time.

For information on the exact version of HICUM/L2 that is available in (commercial) circuit simulators the reader is referred to the respective EDA company websites.

#### **Acknowledgments**

Many individuals have contributed to the development of HICUM through various activities such as valuable feedback and model testing. It is impossible to list everybody who in some way participated in the model related development over the past 30 years. A long list of contributors can be found though in [27].

© M. Schroter 10/8/15 6

# 2 Model equations

### 2.1 Equivalent circuit

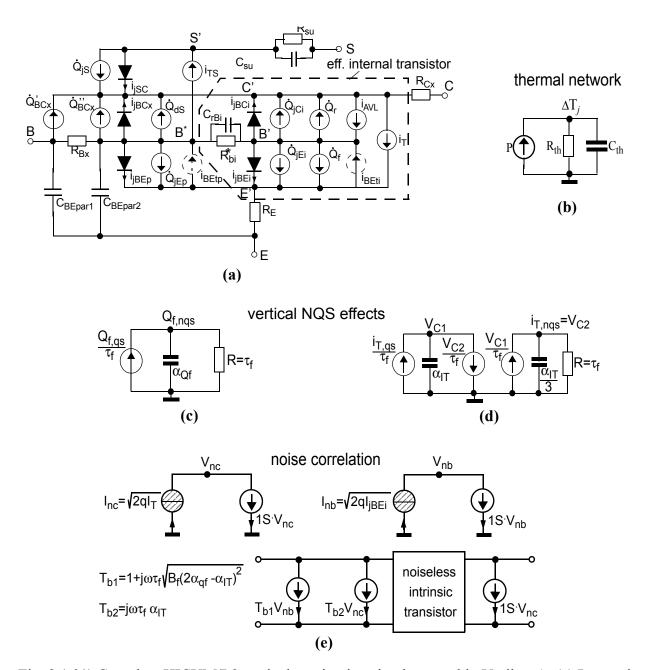

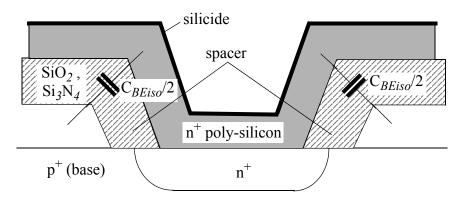

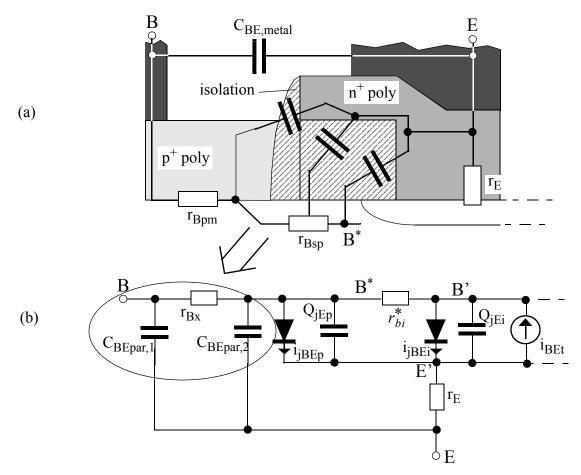

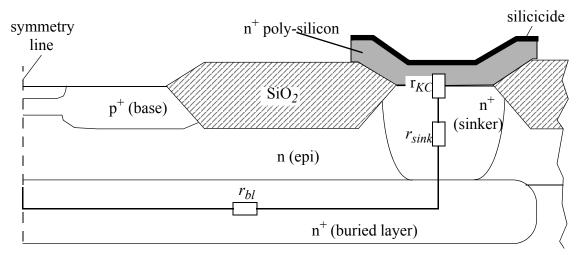

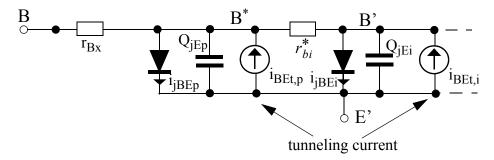

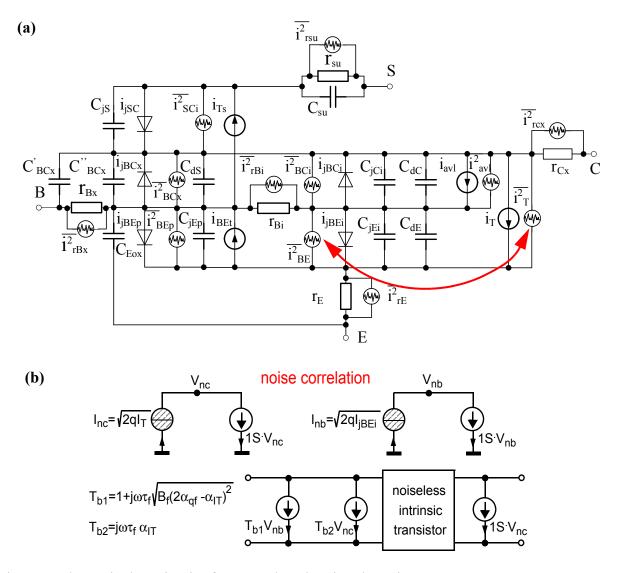

Compared to the SGPM the equivalent circuit (EC) of HICUM/Level2 contains two additional circuit nodes, namely B\* and S' in Fig. 2.1.0/1. The node B\*, which separates the operating point dependent internal base resistance from the operating point independent external component, is required to take into account emitter periphery effects, which can play a significant role in modern transistors. This node is also employed for an improved modelling of the distributed nature of the external base-collector (BC) region by splitting the external BC capacitance  $C_{BCx}$  over  $r_{Bx}$  in the form of a  $\pi$ -type equivalent circuit for the corresponding RC transmission line(s). As a further advantage of introducing the node B\*, high-frequency small-signal emitter current crowding can be correctly taken into account by the capacitance  $C_{rBi}$ . An emitter-base isolation capacitance  $C_{BEpar}$ , that becomes significant for advanced technologies with thin spacer or link regions, as well as a BC oxide capacitance  $C_{BCpar}$ , which is included in the  $C_{BCx}$  element, are taken into account.

In contrast to other models, the influence of the internal collector series resistance is (partially) taken into account by the model equations for the transfer current  $i_T$  and the minority charge which is represented by the elements  $C_{dE}$  and  $C_{dC}$  in Fig. 2.1.0/1. As a consequence, the collector terminal C' of the internal transistor is (physically) located at the end of the epitaxial (or n-well) collector region. This approach not only avoids additional complicated and computationally expensive model equations for an "internal collector resistance" but also saves one node. The chosen approach has been demonstrated to be accurate for a wide range of existing bipolar technologies (cf. [27]).

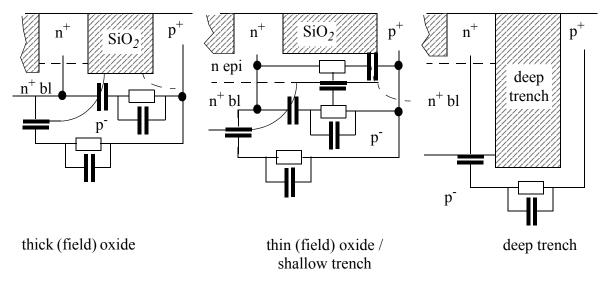

The reliable design of high-speed circuits often requires the consideration of the coupling between the buried layer and the substrate terminal S. Since the substrate material consists of both a resistive and capacitive component, as a first (rough) approach a substrate network with a resistance  $r_{Su}$  and a capacitance  $C_{Su}$  is introduced, leading to the "internal" substrate node S\*. Note that an accurate description of intra-device substrate usually requires a more sohpisticated equivalent circuit which depends on the transistor configuration, employed technology and frequency range though.

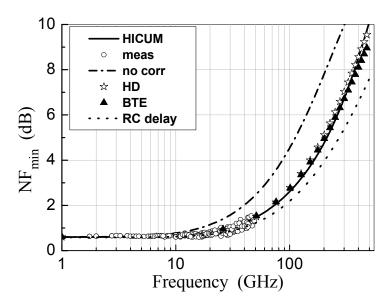

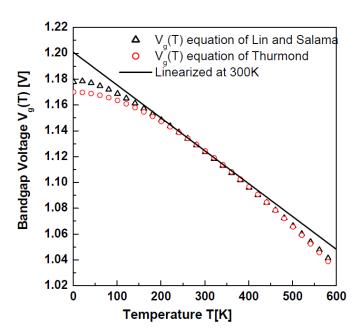

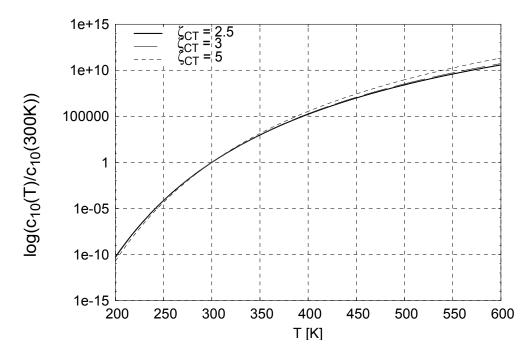

Fig. 2.1.0/1:Complete HICUM/L2 equivalent circuit as implemented in Verilog-A. (a) Large-signal equivalent circuit. The external BC capacitance consists of a depletion and a bias independent parasitic capacitance with the ratio  $C_{BCx}/C_{BCx}$  being adjusted with respect to proper modelling of the h.f. behavior. (b) Thermal network used for self-heating calculation. (c), (d) Adjunt networks for vertical NQS effects. (e) Adjunt networks for correlated high-frequency noise. The internal transistor (index i) is defined by the region under the emitter which is assigned an effective emitter width and area, respectively, in order to retain a one-transistor model with an as simple as possible equivalent circuit topology as well as a sound physical background. The index "p" ("x") indicates elements representing the perimeter (external) transistor region(s).

A possibly existing substrate transistor has been taken into account by using a simple transport model. Like in the SGPM, this can also be realized by a subcircuit (cf. Section 2.12) and setting  $r_{Su}$  and  $C_{jS}$  to zero in the HICUM equivalent circuit. In advanced bipolar processes, the emitter terminal of the substrate transistor (B\*) moves towards the (npn) base contact (B) which makes the external realization of such a parasitic transistor by a subcircuit even easier. The substrate transistor - if it is not avoided by proper layout measures - only turns on for operation at very low CE voltages ("very" hard saturation).

The physical meaning and modelling of all EC elements in Fig. 2.1.0/1 is discussed below in more detail. The description in the following text is given for an npn transistor, which is the most widely used type of bipolar transistors. For vertical pnp transistors, the model can be applied by interchanging the signs of terminal voltages and currents. Lateral pnp transistors can be described by a composition of HICUM/L2 models but usually a subcircuit consisting of three simple transport models (e.g. HICUM/L0) is considered to be more appropriate.

### 2.2 Quasi-static transfer current

The transfer current of a vertical homo- and hetero-junction bipolar transistor can be described by a generalized form of the ICCR that can also be extended to 2D and 3D transistor structures with narrow emitter stripes or very small contact windows. The various steps to arrive at the final equation for the transfer current  $i_T$  are outlined below, demonstrating the modular structure of the model equations. For a detailed derivation of the GICCR the reader is referred to [27].

#### A. Basic formulation

The result of the one-dimensional (1D) GICCR is

$$i_T = \frac{c_{10}}{Q_{p,T}} \left[ \exp\left(\frac{v_{B'E'}}{V_T}\right) - \exp\left(\frac{v_{B'C'}}{V_T}\right) \right]$$

(2.2.0-1)

with the constant

$$c_{10} = (qA_E)^2 V_T \overline{\mu_{nB} n_{iB}^2}. {(2.2.0-2)}$$

$v_{B'E'}$  and  $v_{B'C'}$  are the (time dependent) terminal voltages of the 1D transistor if the integration lead-

ing to the modified hole charge,  $Q_{p,T}$ , is performed throughout the total 1D transistor, i.e. between its emitter and collector contact. The term  $\overline{\mu_{nB} n_{iB}^2}$  is an average value for the base region.

$Q_{p,T}$  consists of a weighted sum of charges,

$$Q_{p,T} = Q_{p0} + h_{jEi}Q_{jEi} + h_{jCi}Q_{jCi} + Q_{f,T} + Q_{r,T}, \qquad (2.2.0-3)$$

The charge formulations designated with the index "T" result when the transfer current is derived from the transport equation and hetero-junctions as well as current spreading are included. The hole charge at thermal equilibrium,  $Q_{p0}$ , is a model parameter.  $Q_{jEi}$  and  $Q_{jCi}$  are the depletion charges stored within the BE and BC junction.  $Q_{f,T}$  and  $Q_{r,T}$  are (weighted) forward and reverse minority charges stored in the total (1D) transistor. The various components in the minority charges and the weighting factors will be discussed in more detail later.

The correspondence to the conventional model formulation can be maintained by realizing that the usual collector saturation current is simply given by

$$I_S = \frac{c_{10}}{Q_{p0}} , \qquad (2.2.0-4)$$

so that (2.2.0-1) can also be written in normalized form:

$$i_T = \frac{I_S}{Q_{p,T}/Q_{p0}} \left[ \exp\left(\frac{v_{B'E'}}{V_T}\right) - \exp\left(\frac{v_{B'C'}}{V_T}\right) \right] . \tag{2.2.0-5}$$

Mathematically,  $i_T$  in (2.2.0-1) can be split into a "forward" component,

$$i_{Tf} = \frac{c_{10}}{Q_{n,T}} \exp\left(\frac{v_{B'E'}}{V_T}\right)$$

(2.2.0-6)

and a "reverse" (better to say inverse) component,

$$i_{Tr} = \frac{c_{10}}{Q_{p,T}} \exp\left(\frac{v_{B'C'}}{V_T}\right) ,$$

(2.2.0-7)

which will be referred to in the discussion below. Physically,  $i_{Tf}$  represents the electron current

flowing from emitter to collector at forward operation at  $\exp(V_{C'E}/V_T) >> 1$ . Analogously,  $i_{Tr}$  represents the electron current flowing from collector to emitter at inverse operation with  $\exp(-V_{C'E}/V_T) >> 1$ . This separation of  $i_T$  simplifies both the implementation of the solution of the non-linear transfer current formulation as well as the modelling of the minority charge components.

# B. Extension to the 2D (3D) case and influence of internal base resistance

The 1D transistor structure can be transformed into a 2D or 3D structure by multiplying all area specific 1D model parameters with the emitter area of the transistor. This defines the internal transistor, i.e. the structure under the emitter window. As a result, the lateral voltage drop caused by the base current has to be taken into account for calculating  $v_{B'E'}$  and  $v_{B'C'}$  in (2.2.0-1). This requires an appropriate definition and model for the internal base resistance by which then  $v_{B'E'}$  and  $v_{B'C'}$  are becoming "averaged" terminal voltages to ensure a correct description of the electrical (terminal) characteristics of the internal transistor.

#### C. Emitter periphery injection

The carrier injection at the emitter periphery junction and the corresponding transfer current component through the external base can be taken into account by defining an effective electrical emitter width  $b_E$  and length  $l_E$ , which are usually larger than the emitter window dimensions. This results in an effective size for the internal transistor in the 2D and 3D case with the effective emitter area  $A_E$ . By multiplication of all area specific 1D model parameters with  $A_E$  (rather than  $A_{E0}$ ) it can be shown, that (2.2.0-1) can then be directly applied without any loss of accuracy at low current densities. At high current densities, however, this approach can become less accurate, and another extension is usually required which will be discussed later.  $v_{B'E'}$  and  $v_{B'C'}$  are now the terminal voltages of the effective internal transistor (cf. Fig. 2.1.0/1), and the components  $Q_{jEi}$  and  $Q_{jCi}$  in the charge  $Q_{p,T}$  are now defined for the effective internal transistor.

Besides the lateral scalability of the model, the major advantages of this approach are that (i) a single equation can be used throughout the total operating region and (ii) a single transfer current source element can be used in the EC (Fig. 2.1.0/1) to describe even transistors with strong 2D and 3D effects.

#### D. Heterojunction bipolar transistors (HBTs)

The generalized ICCR results in the following expression for the weighted minority charge

$$Q_{f,T} = h_{f0}Q_{f0} + h_{fE}\Delta Q_{Ef} + \Delta Q_{Bf} + h_{fC}\Delta Q_{Cf}$$

(2.2.0-8)

with  $Q_{f0}$  as low-current charge component, and  $\Delta Q_{Ef}$ ,  $\Delta Q_{Bf}$ ,  $\Delta Q_{Cf}$  as the actual minority charges in the neutral emitter, base, collector.  $\Delta Q_{Cf}$  can include bias dependent lateral current spreading (see later). The weighing factors  $h_{f0}$ ,  $h_{fE}$  and  $h_{fC}$  as well as  $h_{jEi}$  and  $h_{jCi}$  in (2.2.0-3) are given by the differences and grading of the bandgap between the various transistor regions in a HBT. Note, that  $Q_{f,T}$  is generally *not equal to the stored minority charge*  $Q_f$  used during dynamic operation. The charge components of  $Q_{f,T}$  are discussed in ch. 2.3.

Assuming a linear bandgap change in the base with the grading coefficient  $a_G$ , the model parameter  $h_{jci}$  can be expressed analytically as

$$h_{jCi} \approx \exp\left(-\frac{a_G w_{B0}}{V_T}\right) \tag{2.2.0-9}$$

with  $w_{B0}$  as the neutral base width in equilibrium. The corresponding factor for the BE charge,  $h_{jEi}$ , is close to 1 for Si-based processes, but is usually larger than 1 for (SiGe) HBTs.

Bandgap grading in the base emitter space charge region and the corresponding reduction of the transconductance is modeled by a bias dependence of  $h_{iEi}$  [29]

$$h_{jEi}(v_{B'E'}) = h_{jEi0} \frac{\exp(u) - 1}{u}$$

(2.2.0-10)

with the auxiliary variable

$$u = a_{hjEi} \left[ 1 - \left( 1 - \frac{v_j}{V_{DEi}} \right)^{z_{Ei}} \right]. \tag{2.2.0-11}$$

Here,  $h_{jEi0}^*$  and  $a_{hjEi}$  are model parameters for the value for the weight factor at zero bias and the slope of the bias dependence.  $V_{DEi}$  and  $z_{Ei}$  are already existing parameters describing the bias dependence of the corresponding capacitance  $C_{jEi}$  (cf. 2.4.1).

The parameter  $a_{hiEi}$  is related to the grading in the base. It can be approximated by

<sup>\*.</sup> In order the allow backward compatibility, the parameter  $h_{jEi0}$  is still called  $h_{jEi}$  in the model card.

$$a_{hjEi} = \frac{w_{BE,\,0}}{a_{ni}} \tag{2.2.0-12}$$

with the BE SCR at equilibrium,

$$w_{BE, 0} = x_{p0} - x_{jE} = \sqrt{\frac{2\varepsilon}{q} \frac{N_E V_{DEi}}{N_B (N_B + N_E)}},$$

(2.2.0-13)

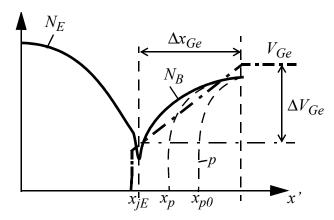

based on the parameters given in Fig. 2.2.0/2 and  $a_{ni} = \Delta x_{Ge} V_T / \Delta V_{Ge}$ .

Fig. 2.2.0/2: Sketch of the internal base emitter region of a HBT with graded bandgap.

Towards and beyond  $V_{DEi}$ , the voltage  $v_{B'E'}$  is limited by

$$v_{B'E'upp} = \frac{V_{DEi} - v_{B'E'}}{r_{h_{iEi}}V_T}$$

and  $v_{j,upp} = V_{DEi} - r_{h_{jEi}}V_T \frac{x_{upp} + \sqrt{x_{upp}^2 + a_{fi}}}{2}$  (2.2.0-14)

with the model parameter  $r_{hjEi}$  and the smoothing constant  $a_{fi}$ = 1.921812. The parameter can be used for smoothing the onset of  $Q_{f,T}$ . The discontinuity at  $v_{B'E'}$ =0 is avoided by

$$v_{B'E'low} = \frac{v_{j,upp} - V_T}{V_T}$$

and  $v_j = V_T \left( 1 + \frac{x_{low} + \sqrt{x_{low}^2 + a_{fi}}}{2} \right)$ . (2.2.0-15)

The weight factors [27]

$$h_{fE} = \frac{\overline{\mu_{nB} n_{iB}^2}}{\mu_{nE} n_{iE}^2}$$

and  $h_{fC} = \frac{\overline{\mu_{nB} n_{iB}^2}}{\mu_{nC} n_{iC}^2}$  (2.2.0-16)

are model parameters that take into account the different values for effective intrinsic carrier concentration  $n_i$  and mobility  $\mu_n$  of the neutral transistor regions. The factors  $h_{jCi}$ ,  $h_{fE}$ , and  $h_{fC}$  are considered to be model parameters in order to make the model applicable also in cases where the doping concentrations and other physical values are unknown.

For SiGe heterojunction transistors,  $h_{fC}$  can be significantly larger than 1 while  $h_{jCi}$  is less than 1, explaining the larger Early voltages measured in those transistors. In contrast, for most homojunction transistors these parameters assume values close to 1 although they are becoming more relevant, too, in advanced homojunction transistors due to high-doping effects.

For HBTs, such as those fabricated in III-V semiconductors, that contain a significant energy difference in the conduction band, transport effects such as thermionic emission and tunneling may have to be accounted for. There are various ways of doing this which differ in complexity and, therefore, convergence rate and simulation time. For the present model, the most simple approach has been adopted by introducing a non-ideality coefficient  $m_{Cf}$  in the forward component of the transfer current:

$$i_{Tf} = \frac{c_{10}}{Q_{p, T}} \exp\left(\frac{v_{B'E'}}{m_{Cf}V_{T}}\right).$$

(2.2.0-17)

This approach is believed to offer sufficient flexibility for practical purposes, while keeping down additional computational burden.

#### E. High current densities

Earlier investigations of a variety of doping profiles have shown that (2.2.0-1) becomes less accurate at high collector current densities due to current spreading in the (epitaxial) collector. This 2D/3D effect can also be taken into account as a physics-based expression by using the GICCR and by applying the same methodology as described in.

Older versions of HICUM contain a simplified modelling of this effect by replacing the constant  $c_{10}$  with the empirical function  $c_1 = c_{10}(1 + i_T/I_{Ch})$  in which  $I_{Ch}$  is a model parameter that is (rough-

ly) proportional to the emitter area. In the presently implemented version, the simplified description is still maintained, but a numerically more stable expression is being used:

$$c_1 = c_{10} \left( 1 + \frac{i_{Tf1}}{I_{Ch}} \right) . {(2.2.0-18)}$$

with the 1D forward transfer current:

$$i_{Tf1} = \frac{c_{10}}{Q_{p,T}} \exp\left(\frac{v_{B'E'}}{m_{Cf}V_T}\right) = I_S \frac{Q_{p0}}{Q_{p,T}} \exp\left(\frac{v_{B'E'}}{m_{Cf}V_T}\right). \tag{2.2.0-19}$$

For  $Q_{r,T}$  the actual charge  $Q_r$  is being used.

#### F. Final transfer current model formulation

The "forward" component defined in (2.2.0-6) is repeated here with the modifications in (2.2.0-17) and (2.2.0-18):

$$i_{Tf} = \frac{c_1}{Q_{p,T}} \exp\left(\frac{v_{B'E'}}{m_{Cf}V_T}\right).$$

(2.2.0-20)

The "reverse" (better to say inverse) component remains identical to (2.2.0-7); in the latter, the influence of collector current spreading at forward operation is not included, i.e.  $c_I = c_{I0}$ . (2.2.0-20) can be re-arranged to give an *explicit* expression for the forward transfer current,

$$i_{Tf} = i_{Tf1} \left( 1 + \frac{i_{Tf1}}{I_{Ch}} \right)$$

(2.2.0-21)

The total transfer current is then

$$i_T = i_{Tf} - i_{Tr}$$

(2.2.0-22)

At high reverse bias across either junction, the respective space-charge region can extend throughout the whole base region (base punch-through or reach-through effect). As a result,  $Q_{p,T}$  would become zero or even less than zero which would cause numerical problems. This situation

is most likely to occur at low current densities, where the (always positive) minority charge is negligible. Therefore, in HICUM the hole charge at low current densities,

$$Q_{pT,j} = Q_{p0} + h_{jEi}Q_{jEi} + h_{jCi}Q_{jCi}, \qquad (2.2.0-23)$$

is limited to a positive value  $Q_{B,rt} = 0.05Q_{p0}$ , using a smoothing function, and is replaced by

$$Q_{pT, low} = Q_{B, rt} \left( 1 + \frac{x + \sqrt{x^2 + a}}{2} \right) \quad with \quad x = \frac{Q_{pT, j}}{Q_{B, rt}} - 1$$

(2.2.0-24)

and a=1.921812 which reproduces the values of the former exponential smoothing function. Compared to version 2.1, only the exponential smoothing function in  $Q_{pT,low}$  has now been replaced by a hyperbolic smoothing function. Also, the previous conditional statement, which turned on the evaluation of the smoothing function for  $Q_{pT,j} < 0.6Q_{p0}$  has been removed to avoid slight inconsistencies in the calculated values and, especially, the associated derivatives. For the usual operating range with  $Q_{pT,j}/Q_{p0} > 1$ , the difference  $Q_{pT,low}-Q_{p,j}$  is much smaller than  $10^{-6}Q_{p0}$ , so the smoothing and the associated computational effort could be skipped in the code.

Also note that the effect of base reach-through is extremely unlikely, so that any additional (numerical) effort to take into account the physical mechanisms occurring under these circumstances does not seem to be justified for a compact model.

In general, the GICCR is a non-linear implicit equation for either  $i_T$  or  $Q_{p,T}$ , respectively. Since  $Q_{p,T}$  is the common variable in both current components  $i_{Tf}$  and  $i_{Tr}$ , the GICCR is solved in HICUM for  $Q_{p,T}$  by employing Newton-Raphson iteration\*. However, as long as  $Q_{f,T}$  and  $Q_r$  are linearly varying functions of the respective current, i.e. the transit times are current *independent*, the GIC-CR reduces to a quadratic equation, with an explicit solution for  $Q_{p,T}$  (assuming  $c_1 = c_{10}$  at low current densities)

$$Q_{p,T} = \frac{Q_{pT,low}}{2} + \sqrt{\left(\frac{Q_{pT,low}}{2}\right)^2 + \tau_{f0}c_{10}\exp\left(\frac{v_{B'E'}}{m_{cf}V_T}\right) + \tau_{r}c_{10}\exp\left(\frac{v_{B'C'}}{V_T}\right)}$$

(2.2.0-25)

<sup>\*.</sup>In the SGPM, the solution is obtained by significant simplifications of the minority charge terms, leading to an (explicit) quadratic equation. Such an approach is physically consistent and accurate only at low current densities.

with  $Q_{p,low}$  from (2.2.0-24). Inserting the above solution into  $i_{Tf}$  and  $i_{Tr}$  and adding the minority charge terms provide quite a useful *initial guess* for the Newton iteration at higher current densities:

$$Q_{p,T,initial} = Q_{pT,low} + \tau_{f0} i_{Tf} + \tau_r i_{Tr} . \qquad (2.2.0-26)$$

For the practical implementation of the GICCR the reader is referred to the model code.

# 2.3 Minority charge, transit times, and diffusion capacitances

The minority charge is divided into a "forward" and a "reverse" (or inverse) component. The forward component,  $Q_f$ , is considered to be dependent on the forward transfer current,  $i_{Tf}$ , while the reverse component,  $Q_r$ , is considered to be dependent on the reverse transfer current,  $i_{Tr}$ . The large-signal charge components can be determined by integrating the respective small-signal transit times, defined as

$$\tau = \frac{dQ}{dI} \tag{2.3.0-27}$$

rather than  $\tau = Q/I$ .

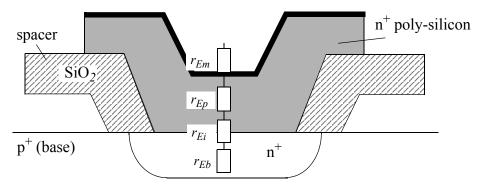

#### 2.3.1 Minority charge component controlled by the forward transfer current

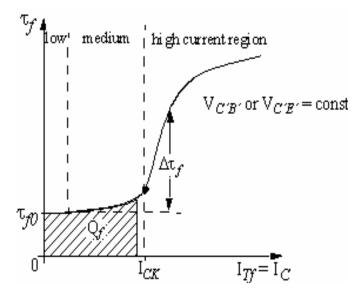

The operating point dependent minority charge stored in a forward biased (vertical) transistor can be determined from the transit time  $\tau_f$  by simple integration (cf. Fig. 2.3.1/1),

$$Q_f = \int_0^{i_{T_f}} \tau_f \, di \quad . \tag{2.3.1-1}$$

<u>Fig. 2.3.1/1:</u> Illustration of the forward minority charge and transit time as a function of current and definition of the bias regions.

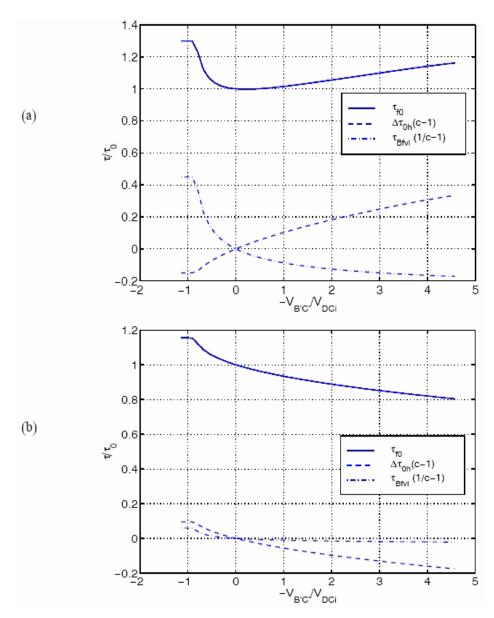

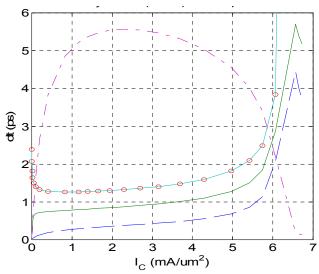

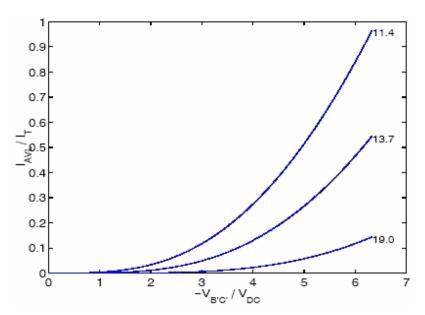

$\tau_f$  can be extracted from the measured transit frequency vs. d.c. collector current  $I_C$  (= $I_T$ ) at forward operation for different voltages  $v_{CE}$  or  $v_{BC}$  as a parameter. The current and voltage dependent transit time is modelled in HICUM by two components,

$$\tau_f(v_{CE'}, i_{Tf}) = \tau_{f0}(v_{B'C}) + \Delta \tau_f(v_{CE'}, i_{Tf}),$$

(2.3.1-2)

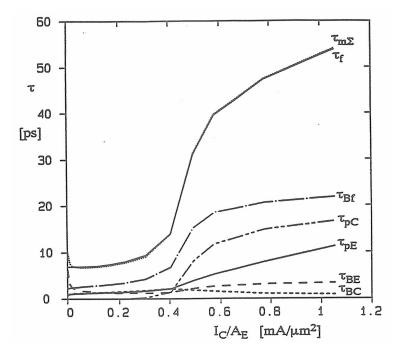

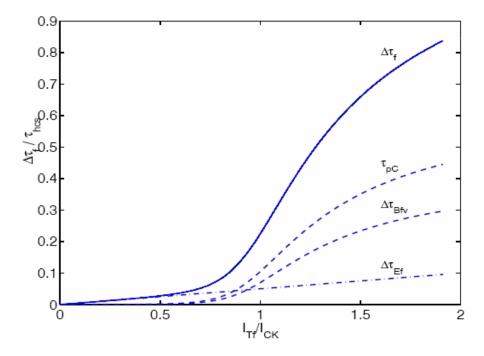

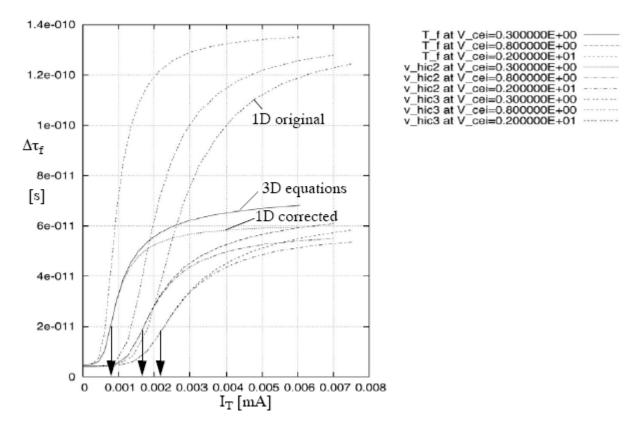

where  $\tau_{f0}$  is the low-current transit time, and  $\Delta \tau_f$  represents the increase of the transit time at high collector current densities. Fig. 2.3.1/2 shows the typically observed behavior of  $\tau_f$  and its various components, for which physics-based equations will be given later in this chapter. It is important to note, that the sum of all physically (from carrier densities) calculated storage times,  $\tau_{m\Sigma}$ , equals the transit time  $\tau_f$ , that is extracted from small-signal results using the measurement method.

Fig. 2.3.1/2: Charge storage and transit time components vs. collector current density. The components  $\tau_{Bf}$ ,  $\tau_{pC}$ ,  $\tau_{pE}$ ,  $\tau_{BE}$ ,  $\tau_{BC}$ , and  $\tau_{m\Sigma}$  were calculated from 1D device simulation, while  $\tau_{B}$  was extracted from small-signal simulations and  $f_{T}$  using the measurement method.

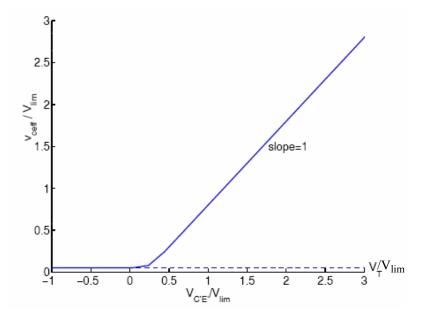

The minority charge model in HICUM uses an "effective" collector voltage

$$v_{ceff} = V_T \left[ 1 + \frac{u + \sqrt{u^2 + a_{vceff}}}{2} \right] \quad \text{with the argument} \quad u = \frac{v_c - V_T}{V_T}$$

(2.3.1-3)

with

$$v_c = v_{CE} - V_{CEs} \approx V_{DCi} - v_{B'C}$$

(2.3.1-4)

The value of the constant  $a_{vceff}$  (= 1.921812) has been adjusted to yield the same results as the exponential smoothing formulation (used in the previous version) and, thus, is not a model parameter. The internal CE saturation voltage  $V_{C'E's}$  ( $\approx V_{DEi}$ - $V_{DCi}$ ) is a model parameter. The smoothing function for  $v_{ceff}$  has been implemented in order to provide a smooth behavior of the critical current (see later) and the forward minority charge for very small and negative values of  $v_c$ . As Fig. 2.3.1/3 shows,  $v_{ceff}$  is equal to  $v_c$  for values larger than about  $2V_{C'E's}$  and approaches the thermal voltage  $V_T$  as the limit for negative values.

The transit time and minority charge model used in HICUM and its derivation are discussed in detail in [27]. In this text, the most important equations and their physical meaning are summarized.

<u>Fig. 2.3.1/3:</u> Normalized effective collector voltage vs. normalized (internal) collector voltage showing the behaviour of the smoothing function.

#### A. Low-current densities

The low-current component  $\tau_{f0}$  depends on the collector-base (or collector-emitter voltage) only,

$$\tau_{f0}(v_{B'C}) = \tau_0 + \Delta \tau_{0h}(c-1) + \tau_{Bvl} \left(\frac{1}{c} - 1\right)$$

(2.3.1-5)

with the normalized internal BC depletion capacitance  $1/c = C_{jCi,t}(V_{B'C'})/C_{jCi0}$ . Note, that  $C_{jCi,t}$  is evaluated for the same model parameters as the internal BC depletion capacitance  $C_{jCi}$ , but with infinite punch-through voltage in order to roughly take into account the impact of the bias dependent space-charge region moving into the base and buried layer beyond the punch-through voltage.

The first time constant in (2.3.1-5),  $\tau_0$ , represents the sum of voltage independent components of various transistor regions at  $V_{B'C'}=0$ ; this condition already defines how to extract its value. The second term represents the net voltage dependent change caused by the Early-effect and the transit time through the BC space charge region: for  $\Delta \tau_{0h} < 0$  the Early effect dominates while for  $\Delta \tau_{0h} > 0$  the transit time increase caused by the widening of the BC space charge region at large voltages dominates. The third term takes into account the finite carrier velocity in the BC space charge region resulting in a carrier jam at low  $V_{C'E'}$  voltages.

Fig. 2.3.1/4 shows two examples for the voltage dependence of the low-current transit time and its two voltage dependent components. The axis values have been normalized to the model parameters  $\tau_0$  and  $V_{DCi}$ , respectively. The upper figure (a) contains a behavior that is (more) typical for a relatively slow high-voltage transistor, which is characterized by a relatively wide and low-doped collector region under the emitter. In this case,  $\tau_{f0}$  increases with increasing  $V_{C'E'}$  (= $V_{B'E'}$ - $V_{B'C'}$ ) due to the widening of the BC space charge region. Towards very low  $V_{C'E'}$  the drift velocity within the BC space charge region decreases, and the respective (third) term in (2.3.1-5) dominates the voltage dependence, which leads again to an increase of  $\tau_{f0}$  and to a minimum around  $V_{B'C'}$ =0.

The lower figure (b) shows the typical behaviour for a high-speed transistor with, e.g., a selectively implanted collector and a thin base. With increasing reverse bias, the BC space charge region does extend noticeably also into the base, resulting in a (slightly) negative value of  $\Delta \tau_{0h}$  and a decrease of the respective component. Therefore,  $\tau_{00}$  decreases with increasing  $V_{C'E'}$ .

The respective low-current forward minority charge is simply given by

$$Q_{f0} = \tau_{f0} i_{Tf} . {(2.3.1-6)}$$

<u>Fig. 2.3.1/4:</u> Normalized low-current transit time and its components as a function of normalized (internal) BC voltage: (a) for a "high-voltage" transistor ( $\tau_0$ =10ps,  $\Delta\tau_{0h}$ =2.5ps,  $\tau_{Bfvl}$ =3ps), (b) for a "high-speed" transistor ( $\tau_0$ =2.5ps,  $\Delta\tau_{0h}$ =-0.4ps,  $\tau_{Bfvl}$ =0.1ps).

#### B. Medium and high current densities

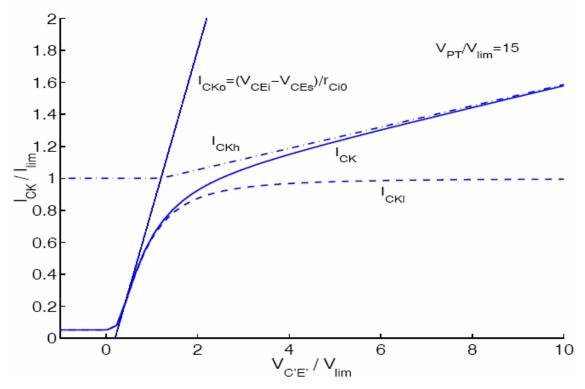

At medium current densities, the electric field at the BC junction starts to decrease, and the BC junction region becomes quasi-neutral at high current densities. This is often called Kirk-effect [3]. In HICUM, the onset of high-current effects is characterized by the critical current

$$I_{CK} = \frac{v_{ceff}}{r_{Ci0}} \frac{1}{\left(1 + \left(\frac{v_{ceff}}{V_{lim}}\right)^{\delta_{ck}}\right)^{1/\delta_{ck}}} \left[1 + \frac{x + \sqrt{x^2 + a_{ickpt}}}{2}\right]$$

(2.3.1-7)

with  $x = (v_{ceff} - V_{lim})/V_{PT}$  in the smoothing function that connects the cases of low and high electric fields in the collector, and with the constant  $a_{ickpt} = 10^{-3}$ .

The other (model) parameters are the internal collector resistance at low electric fields,

$$r_{Ci0} = \frac{w_C}{q\mu_{nC0}N_{Ci}A_E} \frac{1}{f_{cs}} , \qquad (2.3.1-8)$$

the voltage defining the boundary between low and high electric fields in the collector,

$$V_{lim} = \frac{v_{sn}}{\mu_{nC0}} w_C , \qquad (2.3.1-9)$$

and the (collector) punch-through voltage

$$V_{PT} = \frac{qN_{Ci}}{2\varepsilon} w_C^2 . {(2.3.1-10)}$$

As the above relations show,  $I_{CK}$  depends on the electron saturation drift velocity,  $v_{sn}$ , and the electron low-field mobility,  $\mu_{nC0}$ , as well as on width  $w_C$  and (average) doping  $N_{Ci}$  of the internal collector. The current spreading factor  $f_{cs}$ , which is discussed in chapter 2.16, facilitates lateral scaling and is calculated by TRADICA (or any other parameter generation program). Despite their physical relationship,  $r_{Ci0}$ ,  $V_{lim}$  and  $V_{PT}$  are considered to be model parameters in order to offer a more flexible parameter extraction and broader application of the model. However, their physics-based relationship is very useful for temperature and statistical modelling.

<u>Fig. 2.3.1/5:</u> Normalized critical current  $I_{CK}$  vs. normalized internal CE voltage and related single components:  $I_{CKl} = (v_{ceff}/r_{Ci0})/\sqrt{1 + (v_{ceff}/V_{lim})^2}$  from low-voltage theory;  $I_{CKh} = I_{lim} \left[1 + (v_{ceff}-V_{lim})/V_{PT}\right]$  from high-voltage theory with  $I_{lim} = V_{lim}/r_{Ci0}$ .

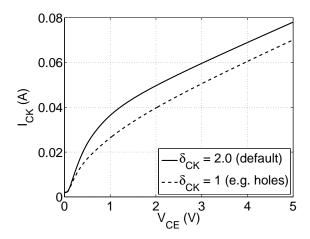

The parameter  $\delta_{ck}$  in (2.3.1-7) can be used for a more flexible description of the field dependent mobility in the collector (e.g. for pnp transistors as shown in Fig. 2.3.1/6).

<u>Fig. 2.3.1/6:</u> Different models for  $I_{CK}$  using the parameter  $\delta_{ck}$ .

The consequence of the changing electric field in the BC junction at medium current densities is, first of all, an increase in the neutral base width and, therefore, in the base component of the transit time; secondly, also the transit time through the BC space charge region may increase, depending on how large the electric field is. Thirdly, the corresponding decrease of the small-signal current gain leads to an increase of the emitter component. Since the current independent part of this component has already been taken into account in  $\tau_{10}$  only the change (increase) has to be modelled,

$$\Delta \tau_{Ef} = \tau_{Ef0} \left( \frac{i_{Tf}}{I_{CK}} \right)^{g_{\tau E}}$$

(2.3.1-11)

with the model parameters  $g_{\tau E}$  and the storage time

$$\tau_{Ef0} = \frac{\tau_{pE0}}{\beta_0} \approx \frac{1}{\beta_0} \left( \frac{w_E}{v_{Ke}} + \frac{w_E^2}{2\mu_{pE}V_T} \right)$$

(2.3.1-12)

which depends on the low-frequency common-emitter small-signal current gain  $\beta_0$  and the hole transit time  $\tau_{pE0}$  in which  $w_E$ ,  $\mu_{pE}$ , and  $v_{Ke}$  are the width, hole mobility, and the effective hole contact recombination velocity of the neutral emitter, respectively. The corresponding charge stored in the neutral emitter is:

$$\Delta Q_{Ef} = \Delta \tau_{Ef} \frac{i_{Tf}}{1 + g_{\tau E}} . \qquad (2.3.1-13)$$

In the neutral collector, minority (hole) charge storage starts only at high current densities. Therefore, the charge difference to its negligible low-current contribution is equal to the total hole charge  $Q_{pC}$  in the collector:

$$\Delta Q_{Cf} = Q_{Cf} = Q_{pC} = \tau_{pCs} i_{Tf} w^2$$

(2.3.1-14)

with the saturation storage time of the neutral collector,

$$\tau_{pCs} = \frac{w_C^2}{4\mu_{nC0}V_T} \ . \tag{2.3.1-15}$$

The normalized injection width,

$$w = \frac{w_i}{w_C} = \frac{i + \sqrt{i^2 + a_{hc}}}{1 + \sqrt{1 + a_{hc}}}$$

(2.3.1-16)

is bias dependent via the variable

$$i = 1 - \frac{I_{CK}}{i_{Tf}} \tag{2.3.1-17}$$

while  $a_{hc}$  is considered to be a model parameter. By using a smoothing function for w rather than the original expression i in (2.3.1-16), the collector charge is made continuously differentiable over the whole bias region. The corresponding collector storage time is given by

$$\Delta \tau_{Cf} = \tau_{Cf} = \tau_{pC} = \frac{dQ_{pC}}{dI_{Tf}} = \tau_{pCs} w^2 \left[ 1 + \frac{2}{\frac{i_{Tf}}{I_{CK}} \sqrt{i^2 + a_{hc}}} \right]$$

(2.3.1-18)

Device simulations for many different processes have shown that the shape of the current dependence of the neutral base component  $\tau_{Bf}$ , is very similar to that of the collector portion  $\tau_{pC}$  due to the coupling of these regions by the carrier density at the BC junction. As a consequence, the bias dependent increase of the base charge at high-current densities is similarly expressed as

$$\Delta Q_{Bf} = \tau_{Bfvs} i_{Tf} w^2 \tag{2.3.1-19}$$

with the saturation storage time reached at high current densities,

$$\tau_{Bfvs} = \frac{w_{Bm}w_C}{2G_{\zeta_i}\mu_{nC0}V_T} \ . \tag{2.3.1-20}$$

$w_{Bm}$  is the metallurgical base width, and  $G_{\zeta i}$  ( $\geq 1$ ) is a factor that depends on the drift field in the neutral base. The corresponding additional base transit time reads

$$\Delta \tau_{Bf} = \frac{d\Delta Q_{Bf}}{dI_{Tf}} = \tau_{Bfvs} \ w^2 \left[ 1 + \frac{2}{\frac{i_{Tf}}{I_{CK}} \sqrt{i^2 + a_{hc}}} \right]. \tag{2.3.1-21}$$

In HICUM, the total storage time constant,

$$\tau_{hcs} = \tau_{pCs} + \tau_{Bfvs} = \frac{w_C^2}{4\mu_{nC0}V_T} + \frac{w_{Bm}w_C}{2G_{\zeta i}\mu_{nC0}V_T} , \qquad (2.3.1-22)$$

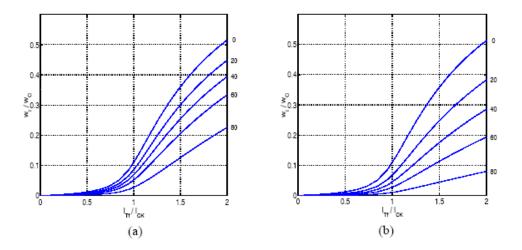

is used as a model parameter to make the model application more flexible and easy to use. As discussed in chapter 2.16, the accurate and physics-based description of collector current spreading and associated lateral scaling at high current densities require a partitioning between base and collector component. For this, the partitioning constant

$$f_{\tau hc} = \frac{\tau_{pCs}}{\tau_{hcs}} = \frac{w_C}{w_C + 2w_{Bm}}$$

(2.3.1-23)

is introduced as model parameter. A value of  $f_{\tau hc}$  between 0 and 1 allows a gradual partitioning, with the 1D expressions given above (i.e. no collector current spreading) being employed for  $f_{\tau hc}$  = 0, while a dominating influence of the collector term (including current spreading) can be taken into account by  $f_{\tau hc} \rightarrow 1$ .

Fig. 2.3.1/7 shows a sketch of the current dependence of the *additional* transit time  $\Delta \tau_f$  and its various components, calculated with the equations given above and using model parameters that are typical for a high-speed process.

In case of negligible collector current spreading (corresponding to 1D current flow), the collector and base component can be lumped together ( $f_{\tau hc} = 0$ ), leading to the expression for the additionally stored minority charge in the base and collector region at high current densities,

$$\Delta Q_{fh} = \Delta Q_{Bf} + Q_{Cf} = \tau_{hcs} i_{Tf} w^{2}$$

(2.3.1-24)

The corresponding increase of the transit time at high-current densities is then given by

$$\Delta \tau_{fh} = \Delta \tau_{Bf} + \tau_{Cf} = \tau_{hcs} w^2 \left[ 1 + \frac{2}{\frac{i_{Tf}}{I_{CK}} \sqrt{i^2 + a_{hc}}} \right] . \tag{2.3.1-25}$$

The 1D current flow is detected by the model if the model parameters LATB and LATL (cf. chapter 2.16) are zero.

Fig. 2.3.1/7: Sketch of normalized transit time  $\Delta \tau_f$  vs. normalized forward collector current  $I_{Tf}$ , including the various components: collector component  $\tau_{pC}$ , additional base component  $\Delta \tau_{Bf}$ , and additional emitter contribution  $\Delta \tau_{Ef}$ .

The total minority charge in the various operating regions, that is used for transient or high-frequency analysis, is then calculated according to (2.3.0-27) and it consists of the following contributions:

$$Q_f = Q_{f0} + \Delta Q_{Ef} + \Delta Q_{fh} \tag{2.3.1-26}$$

while the total forward transit time (or storage time) is given by

$$\tau_f = \tau_{f0} + \Delta \tau_{Ef} + \Delta \tau_{fh} \quad . \tag{2.3.1-27}$$

If the lateral scaling capability is used,  $\Delta Q_{fh}$  and  $\Delta \tau_{fh}$  are composed of their separately calculated base and collector contribution (cf. chapter 2.16). The above equations contain physical and process parameters that facilitate the predictions of the electrical characteristics as a function of process variations.

In SiGe HBTs (and other HBTs with a heterojunction in the BC SCR), a strong increase of the transit time may be observed at the onset of high current effects depending on the location of the heterojunction relative to the junction. The associated BC barrier effect is modeled in HICUM by the current and voltage dependent barrier voltage

$$\Delta V_{cB} = V_{cBar} \exp\left(-\frac{2}{i_{Bar} + \sqrt{i_{Bar}^2 + a_{cBar}^2}}\right)$$

(2.3.1-28)

with the smoothing variable

$$i_{Bar} = \frac{i_{Tf} - I_{CK}}{i_{cBar}} \tag{2.3.1-29}$$

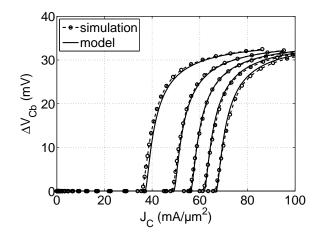

and the model parameters  $V_{cBar}$ ,  $a_{cBar}$  and  $i_{cBar}$ . As shown in Fig. 2.3.1/8, the barrier voltage as obtained by 1D device simulation is modeled very accurately by this equation. Setting  $V_{cBar} = 0$  turns off the entire barrier effect formulation.

Fig. 2.3.1/8: Modeling of the barrier voltage.

Due to the barrier, the charge and transit time of (2.3.1-26) and (2.3.1-27) change to

$$Q_f = Q_{f0} + \Delta Q_{Ef} + \Delta Q_{fh,c} + \Delta Q_{Bf,b}$$

(2.3.1-30)

and

$$\tau_f = \tau_{f0} + \Delta \tau_{Ef} + \Delta \tau_{fh,c} + \Delta \tau_{Bf,b}.$$

(2.3.1-31)

The impact of the BC barrier effect on the base region related mobile charge component is described by

$$\Delta Q_{Bf, b} = \tau_{Bfvs} i_{Tf} \left[ \exp\left(\frac{\Delta V_{cB}}{V_T}\right) - 1 \right]$$

(2.3.1-32)

with  $\tau_{Bfvs} = (1 - f_{\tau hc})\tau_{hCs}$ . The Kirk-effect related collector charge and transit time increase is delayed by the barrier voltage according to

$$\Delta Q_{fh,c} = \tau_{hCs} i_{Tf} w^2 \exp\left(\frac{\Delta V_{cB} - V_{cBar}}{V_T}\right)$$

(2.3.1-33)

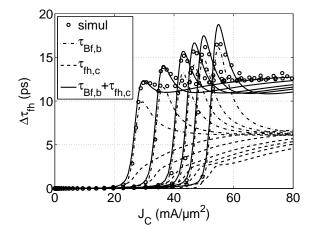

Using above equations, the strong increase of the transit time as well as a possible overshoot is modeled as shown in Fig. 2.3.1/9 for a comparison with 1D device simulation.

Fig. 2.3.1/9: Modeling of the transit time taking the heterojunction effect into account.

Modeling collector current spreading requires the modification of only the collector component  $\Delta Q_{Cf,c}$  of  $\Delta Q_{fh,c}$ , while modeling the barrier related recombination in the base (and associated additional base current) requires an expression for the total additional base charge

$$\Delta Q_{Bf} = \Delta Q_{Bf,b} + \Delta Q_{Bf,c}. \tag{2.3.1-34}$$

Using the parameter  $f_{\tau hc}$  allows to split  $\Delta Q_{fh,c}$  into the two desired components

$$\Delta Q_{Cf,c} = f_{\tau hc} \Delta Q_{fh,c}, \qquad (2.3.1-35)$$

$$\Delta Q_{Bf,c} = (1 - f_{\tau hc}) \Delta Q_{fh,c},$$

(2.3.1-36)

while the sum of the original charges still remains the same:

$$\Delta Q_{fh,c} + \Delta Q_{Bf,b} = \Delta Q_{Cf,c} + \Delta Q_{Bf}$$

(2.3.1-37)

A detailed explanation of these components can be found in [27].

#### 2.3.2 Minority charge component controlled by the inverse transfer current

For forward transistor operation in high-speed applications, the portion of the minority charge which is exclusively controlled by the base-collector voltage is often negligible or only a small fraction of the total minority charge. Therefore, including this charge in  $Q_f$  causes only negligible error in transient operation of transistors in high-speed circuits. For small-signal high-frequency operation in the high-current region, which is a very unusual case, the base-collector voltage controlled charge may be taken into account by including its diffusion capacitance in the total internal base collector capacitance.

Alternatively, the BC diffusion charge can be modelled by the simple relation

$$Q_r = \tau_r i_{Tr} \tag{2.3.2-1}$$

with the inverse transit time  $\tau_r$  as a model parameter.

# 2.4 Depletion charges and capacitances

Modelling of depletion charges  $(Q_j)$  and capacitances  $(C_j)$  as a function of the voltage v across the respective junction is partially based on classical theory that gives within a certain operating range

$$Q_{j} = \int_{0}^{v} C_{j} dv' = \frac{C_{j0} V_{D}}{1 - z} \left[ 1 - \left( 1 - \frac{v}{V_{D}} \right)^{(1 - z)} \right]$$

(2.4.0-2)

and

$$C_{j} = \frac{C_{j0}}{\left(1 - \frac{v}{V_{D}}\right)^{z}} {2.4.0-3}$$

The zero bias capacitance  $C_{j0}$ , the diffusion (or built-in) voltage  $V_D$  as well as the exponent coefficient z are the model parameters. Due to the pole at forward bias, i.e. at  $v=V_D$ , however, the above formula is not yet suited for a compact model from both a numerical and physics-based point of view. The respective modification will be described for the BE depletion capacitance.

At high reverse voltages the epitaxial collector can become fully depleted up to the buried layer. This punch- (or reach-)through effect is also not included in the classical equation above (and in the SGPM). The corresponding extension will be discussed for the BC depletion capacitance.

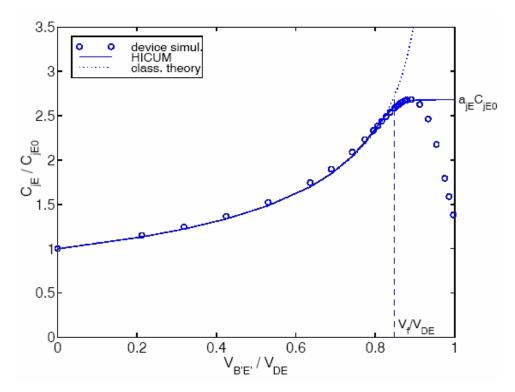

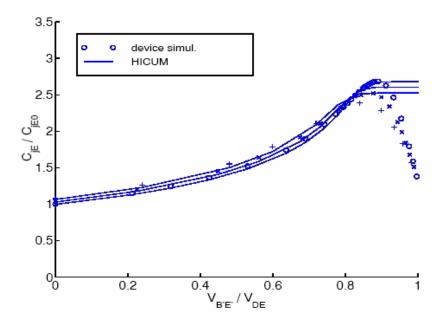

#### 2.4.1 Base-emitter junction

Fig. 2.4.1/1 shows the voltage dependence of a BE depletion capacitance at forward bias. The symbols were obtained from 1D device simulation. The depletion capacitance follows quite well the classical equation up to a certain voltage, which is close to the turn-on voltage of a transistor used for switching applications. In contrast to the classical equation, the capacitance then reaches a maximum within the "practical" operation range of a transistor. Towards very high forward bias, the capacitance even decreases to zero, since the total depletion charge has to be limited from a physical point of view.

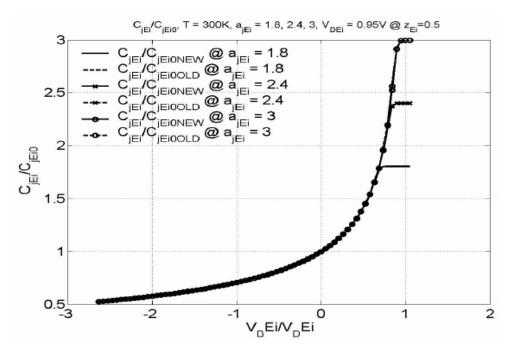

The modified equation employed in HICUM is described below for the example of the internal BE depletion capacitance with the (classical) model parameters  $C_{jEi0}$ ,  $V_{DEi}$ ,  $z_{Ei}$ , and the additional model parameter  $a_{jEi}$ . The latter is defined in Fig. 2.4.1/1 as the ratio of the maximum value to the

zero-bias value and can directly be extracted from  $f_T$  measurements at low current densities (e.g. [2, 27]). As a consequence,  $C_{jEi}$  is kept at its maximum value in HICUM to maintain consistency between measurement and model. Keeping  $C_{jEi}$  constant is also justified, because at high forward bias, i.e. beyond the maximum, the diffusion capacitance becomes orders of magnitude larger than  $C_{jEi}$ . The reverse bias region of the BE depletion capacitance and charge is described by the classical equations.

For modeling the peripheral BE depletion charge and capacitance, the corresponding model parameters  $C_{jEp0}$ ,  $V_{DEp}$ ,  $z_{Ep}$ ,  $a_{jEp}$  as well as the voltage and  $v_{B^*E'}$  have to be inserted.

<u>Fig. 2.4.1/1:</u> Typical dependence of BE depletion capacitance on junction voltage at forward bias: comparison between 1D device simulation, HICUM, classical theory. In addition, characteristic variables used in the model equations have been inserted.

From Fig. 2.4.1/1, the forward bias depletion charge can be composed of a classical portion and a component for medium and large forward bias:

$$Q_{jEi} = \frac{C_{jEi0}V_{DEi}}{1 - z_{Ei}} \left[ 1 - \left(1 - \frac{v_j}{V_{DEi}}\right)^{(1 - z_{Ei})} \right] + a_{jEi}C_{jEi0}(v_{B'E'} - v_j).$$

(2.4.1-1)

The arithmetic overflow at  $V_{DEi}$  is avoided by replacing the junction voltage  $V_{B'E'}$  with the auxil-

iary voltage

$$v_j = V_f - V_T \frac{x + \sqrt{x^2 + a_{fj}}}{2} < V_f$$

(2.4.1-2)

using hyperbolic smoothing and the argument

$$x = \frac{V_f - v_{B'E'}}{V_T}. (2.4.1-3)$$

$V_f$  is the voltage at large forward bias, at which the capacitance of the classical expression intercepts the maximum constant value (cf. Fig. 2.4.1/1):

$$V_f = V_{DEi}[1 - a_{jEi}^{-(1/z_{Ei})}]. (2.4.1-4)$$

$Q_{jEp}$  is calculated similarly.

The depletion capacitance is then calculated from the derivative of the charge yielding

$$C_{jEi} = \frac{C_{jEi0}}{(1 - v_i / V_{DEi})^{z_{Ei}}} \cdot \frac{dv_j}{dv_{B'E'}} + a_{jEi} C_{jEi0} \left(1 - \frac{dv_j}{dv_{B'E'}}\right)$$

(2.4.1-5)

with the derivative of  $v_j$ ,

$$\frac{dv_j}{dv_{B'E'}} = \frac{x + \sqrt{x^2 + a_{fj}}}{2\sqrt{x^2 + a_{fj}}}.$$

(2.4.1-6)

The capacitance is not explicitly coded in the Verilog-A implementation. Instead the derivative of the depletion charge is calculated automatically (symbolically and numerically) where required.

In (2.4.1-6), the value of  $a_{fj}$  can be adjusted to yield results equivalent to the former formulation. If at x = 0, which corresponds to  $v_{B'E'} = V_{f}$ , the exponential and hyperbolic function values for  $v_j$  are forced to be the same, and one obtains

$$a_{fi} = 4 \ln^2(2) = 1.921812.$$

(2.4.1-7)

This is not a model parameter, but a fixed constant within the code. Fig. 2.4.1/2 shows a comparison of the (2.4.1-2) with the old equation of version 2.1. There is no visible difference; the numerically calculated error is below 1.4% for  $a_{iEi} = 3$ , and below 1% for values of 2.4 or lower.

Fig. 2.4.1/2: Base-emitter depletion capacitance calculated with equation (2.4.1-2) with  $a_{jEi}$  as parameter.

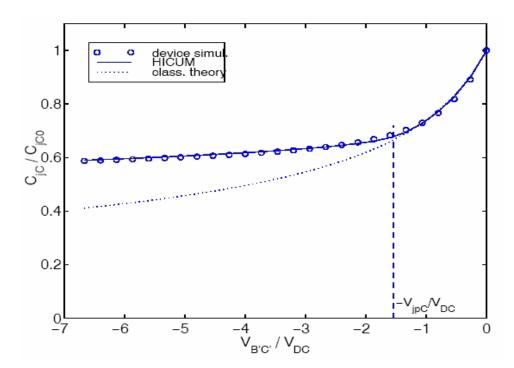

#### 2.4.2 Internal base-collector junction

The BC junction is usually operated at reverse bias. If the internal voltage  $v_{C'B'}$  exceeds the effective punch-through voltage (see later), the epitaxial collector region becomes fully depleted. For an ideal step-like transition from the epitaxial collector to the buried-layer the corresponding capacitance would remain constant (like a plate capacitance). However, in reality the doping concentration increases with only a finite slope towards the maximum buried layer concentration. As a consequence,  $C_{jCi}$  still decreases even beyond punch-through, but with a weaker voltage dependence.

Before the capacitance equation is explained in detail, it is helpful to define a number of variables that are needed in the equations. The effective punch-through voltage is given by

$$V_{jPCi} = V_{PTCi} - V_{DCi} = \frac{qN_{Ci}}{2\varepsilon}w_{Ci}^2 - V_{DCi}$$

, (2.4.2-1)

which is shown in Fig. 2.4.2/1. For flexibility and accuracy reasons as well as in order to simplify and decouple parameter extraction,  $V_{PTCi}$  is considered as a separate model parameter rather than using  $V_{PT}$  from the  $I_{CK}$  formulation. For predictive modeling  $V_{PTCi}=V_{PT}$  is certainly a good initial guess.

<u>Fig. 2.4.2/1:</u> Typical dependence of BC depletion capacitance on junction voltage at reverse bias: comparison between 1D device simulation (symbols), HICUM (solid line), classical theory (dashed line). In addition, characteristic variables used in the model equations have been inserted.

The voltage defining the boundary between the classical expression and the maximum (constant) value at large forward bias was already defined for the BE junction capacitance (cf. Fig. 2.4.1/1); in terms of the respective BC model parameters it reads here as:

$$V_{fCi} = V_{DCi} [1 - a_{jCi}^{-(1/z_{Ci})}] (2.4.2-2)$$

The voltage, at which the transition from medium to large reverse bias (slowly) starts, is defined as

$$V_r = 0.1 V_{jPCi} + 4 V_T (2.4.2-3)$$

In the following, "large reverse" bias is defined as  $v_{BCi} \le -V_{jPCi}$ , "medium" bias is defined as

$V_{jPCi} < v_{BCi} < V_{fCi}$ , and "large forward" bias is defined as  $v_{BCi} \ge V_{fCi}$ .

The depletion capacitance consists of three components,

$$C_{jCi} = C_{jCi, cl} + C_{jCi, PT} + C_{jCi, fb}, (2.4.2-4)$$

which are discussed below in more detail.

$C_{jCi,cl}$  represents the contribution at medium bias,

$$C_{jCi,cl} = \frac{C_{jCi0}}{(1 - v_{j,m} / V_{DCi})^{z_{Ci}}} \cdot \frac{e_{j,r}}{1 + e_{j,r}} \frac{e_{j,m}}{1 + e_{j,m}}$$

(2.4.2-5)

which contains the classical equation as the first term. The last two product terms result from smoothing functions for the respective BC junction voltage, that enable a continuously differentiable transition to the two adjacent bias regions. Like for the BE depletion capacitance, the numerical overflow at large forward bias is avoided by replacing  $v_{B'C'}$  with the auxiliary (smoothed) voltage,  $v_{j,m}$ , defined in (2.4.1-2). The collector punch-through at reverse bias is included by an additional smoothing term,

$$v_{j,r} = V_{fCi} - V_T \ln[1 + e_{j,r}]$$

with  $e_{j,r} = \exp\left(\frac{V_{fCi} - v_{B'C'}}{V_T}\right)$ , (2.4.2-6)

which also contains the actual junction voltage  $v_{B'C'}$ . Analogously to  $C_{jE}$ , the forward bias value (for  $e(v_{j,r}) = 0$ ) is limited to a maximum,

$$C_{jCi,fb} = a_{jCi}C_{jCi0} \frac{1}{1 + e_{j,r}} , \qquad (2.4.2-7)$$

with  $a_{jCi}$  as a constant. The last term is again a continuously differentiable function that enables a smooth transition between large forward and medium bias. Since  $C_{jCi}$  is of little practical relevance and is influenced at high forward bias,  $a_{jCi}$  is set to 2.4 in the code, rather than being a model parameter in order to keep the number of parameters as low as possible.

Finally,  $C_{jCi,PT}$  represents the large reverse bias region around and beyond punch-through,

$$C_{jCi,PT} = \frac{C_{jCi0,r}}{(1 - v_{j,r} / V_{DCi})^{z_{Ci,r}}} \cdot \frac{1}{1 + e_{j,m}}$$

(2.4.2-8)

Here, the first term contains the classical voltage dependence, but now with different parameters  $C_{jCi0,r}$  and  $z_{Ci,r}$ , which model the weak bias dependence under punch-through conditions, and will be discussed later. In this case, the auxiliary voltage is given by the smoothing function

$$v_{j,m} = -V_{jPCi} + V_r \ln[1 + e_{j,m}]$$

with  $e_{j,m} = \exp\left(\frac{V_{jPCi} + v_{j,r}}{V_r}\right)$  (2.4.2-9)

which now depends on the auxiliary voltage  $v_{j,r}$  in order to enable a smooth capacitance and charge behavior over all bias regions. Note, that  $v_{j,r}$  equals  $v_{B'C'}$  at large reverse bias.

The corresponding depletion charge is then obtained by integration of  $C_{jCi}$ ,

$$Q_{jCi} = \underbrace{Q_{jCi,m}}_{\text{medium}} + \underbrace{Q_{jCi,r}}_{\text{reverse}} - \underbrace{Q_{jCi,c}}_{\text{correction}} + \underbrace{a_{jCi}C_{jCi0}(v_{B'C'} - v_{j,r})}_{\text{large forward}}$$

(2.4.2-10)

with the component at medium bias,

$$Q_{jCi,m} = \frac{C_{jCi0}V_{DCi}}{1 - z_{Ci}} \left[ 1 - \left(1 - \frac{v_{j,m}}{V_{DCi}}\right)^{1 - z_{Ci}} \right] , \qquad (2.4.2-11)$$

the component at large reverse bias,

$$Q_{jCi,r} = \frac{C_{jCi0,r}V_{DCi}}{1 - z_{Ci,r}} \left[ 1 - \left(1 - \frac{v_{j,r}}{V_{DCi}}\right)^{1 - z_{Ci,r}} \right] , \qquad (2.4.2-12)$$

and a "correction" component,

$$Q_{jCi,c} = \frac{C_{jCi0,r}V_{DCi}}{1 - z_{Ci,r}} \left[ 1 - \left(1 - \frac{v_{j,m}}{V_{DCi}}\right)^{1 - z_{Ci,r}} \right] , \qquad (2.4.2-13)$$

that results from the integration process. The parameters  $C_{jCi0,r}$  and  $z_{Ci,r}$  in the last two components are required to model the weaker voltage dependence under punch-through conditions, compared

to the voltage dependence at medium bias.  $C_{jCi0,r}$  can be calculated from the punch-through voltage as

$$C_{jCi0,r} = C_{jCi0} \cdot \left(\frac{V_{DCi}}{V_{PTCi}}\right)^{(z_{Ci} - z_{Ci,r})}, \qquad (2.4.2-14)$$

while  $z_{Ci,r}$  is internally set to  $z_{Ci}/4$ . The latter turned out to be a good compromise for the investigated cases. As consequence, both  $C_{jCi0,r}$  and  $z_{Ci,r}$  are only internal parameters and do not have to be extracted and externally specified. If required, however, it would be sufficient to make  $z_{Ci,r}$  a user model parameter.

At high current densities  $C_{jCi}$  becomes also current dependent as discussed, e.g., in [27]. The respective (smooth) expressions for both capacitance and charge require complicated expressions which can increase simulation time significantly. For small-signal applications, a pure voltage dependent model for  $C_{jCi}$  is usually sufficient, since transistors in (small-signal) analog circuits are not operated at high current densities. For large-signal transient applications, however, the influence of a current dependent  $C_{jCi}$  is negligible, especially at higher current densities. Therefore, the current dependence of  $C_{iCi}$  is neglected in the present HICUM version.

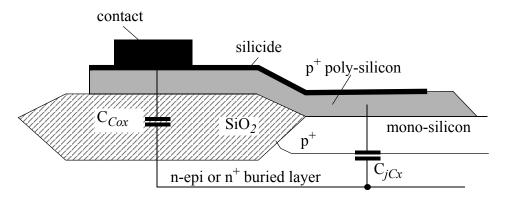

## 2.4.3 External base-collector junction

The total BC capacitance consists of a bias dependent external depletion capacitance,  $C_{jCx}$ , and a bias independent parasitic capacitance  $C_{BCpar}$  (see also Section 2.7). The depletion portion in turn contains a SIC related bottom component, a background doping related bottom component and a perimeter component, that all usually have different voltage dependence and, hence, model parameters. For a compact model, the depletion components are merged into a single element by fitting a single set of model parameters to the overall voltage dependence (e.g. using TRADICA). The resulting capacitance (and charge),  $C_{BCx} = C_{jCx}(v) + C_{BCpar}$ , is then partitioned across the external base resistance  $r_{Bx}$  (cf. Fig. 2.1.0/1) according to a first-order high-frequency approximation of the RC transmission line behaviour of the external base. This merging procedure, which is also required for simpler equivalent circuit structures, reduces the number of model parameters to be specified for the circuit simulator. A possible alternative is to determine the partitioning from measurements of, e.g., high-frequency S-parameters; however, it was found that such a partitioning

factor (strongly) depends on the measurement method and conditions used and, therefore, can assume non-physical values.

The partitioning of the total capacitance  $C_{BCx}$  across  $r_{Bx}$  requires an additional model parameter,

$$f_{BCpar} = \frac{C_{BCx2}}{C_{RCx}} (2.4.3-1)$$

and defines the ratio of the portion at the perimeter base node ("behind"  $r_{Bx}$ ) to the total capacitance. The factor  $f_{BCpar}$  depends on geometry and technology specific parameters (and can be calculated by , e.g., TRADICA). According to (2.4.3-1) the capacitances are split as follows in the present HICUM implementation (cf. Fig. 2.1.0/1):

$$C_{BCx} = C_{BCx1} + C_{BCx2} = (1 - f_{BCpar}) C_{BCx} + f_{BCpar} C_{BCx}$$

(2.4.3-2)

Depending on the values for  $f_{BCpar}$ ,  $C_{BCpar}$  and  $C_{jCx}$  as well as according to the nature of the capacitance components, different cases have to be distinguished. For instance, if  $f_{BCpar} > C_{BCpar}/C_{BCx}$  then part of  $C_{BCpar}$  has to be connected to node B\* (i.e. behind  $r_{Bx}$ ). Since  $C_{BCpar}$  is closest to the base contact, usually the major portion or even its total value has to be connected to the base terminal B. The various cases are taken into account based on the zero-bias depletion capacitance rather than the voltage dependent value in order to reduce arithmetic operation count. The implementation is as shown in Fig. 2.1.4/4.

$$C_{BCx01} = (1-f_{BCpar}) C_{BCx0}$$

$if(C_{BCx01} \ge C_{BCpar}) then$

$C_{BCpar1} = C_{BCpar}$

$C_{BCpar2} = 0$

$C_{jCx01} = C_{BCx01} - C_{BCpar}$

$C_{jCx02} = C_{jCx0} - C_{jCx01}$

$else$

$C_{BCpar1} = C_{BCx01}$

$C_{BCpar2} = C_{BCpar} - C_{BCpar1}$

$C_{jCx01} = 0$

$C_{jCx02} = C_{jCx0}$

$endif$

Fig. 2.4.3/1: Implementation of B-C capacitance partitioning

Since the depletion charge of the external BC junction does not depend on the transfer current, the purely voltage dependent expressions given for  $C_{jCi}$  and  $Q_{jCi}$  can be employed for  $C_{jCx}$  and  $Q_{jCx}$  by simply inserting the model parameters  $C_{jCx0}$ ,  $V_{DCx}$ ,  $z_{Cx}$ , and  $V_{PTCx}$ . The punch-through voltage (and capacitance) of the external collector region is usually different from that of the internal region due to their different epi widths and - in case of a selectively implanted collector - the different doping concentrations in the internal and external region.

## 2.4.4 Collector-substrate junction

The CS depletion charge and capacitance are modelled by the same type of formula as employed for the bottom part of the external BC charge and capacitance. The corresponding model parameters are  $C_{jS0}$ ,  $V_{jS}$ ,  $z_{S}$ , and  $V_{PTS}$ . Taking into account the punch-through effect may be necessary for technologies containing a semi-insulating substrate (layer). For most technologies, however, there is no punch-through effect at the CS junction, and  $V_{PTS}$  can be set to "infinity".

Since the CS junction is modelled by a single element,  $C_{jS}$  contains - from a physical point of view - both the bottom and peripheral portion of that junction; i.e., the model parameters result from merging the corresponding voltage dependent portions (see also Fig. 2.11.0/1).

For certain applications and processes, an additional substrate coupling network in series to  $C_{jS}$  as well as a substrate transistor may be necessary. These extensions are discussed later.

# 2.5 Static base current components

The base current flowing into the emitter can be separated into a bottom and peripheral component. The bottom portion models the current injected across the (effective) emitter area, and the peripheral component models the current injected across the peripheral BE junction. Each of these components contains the current contributions caused by volume (SRH and Auger) recombination, by surface recombination, by tunneling, and by an (effective) interface recombination velocity at the emitter "contact". The physical modelling of all these effects, including e.g. the modulation of the neutral emitter width in advanced and heterojunction bipolar transistors, would require a complicated and computationally time expensive description as well as a significantly increased effort in parameter determination. From a practical application point of view, however, a simpler approach for most of the above mentioned components does exist that is sufficiently accurate.

The following equations describe the d.c. and quasi-static component of the base current, which are applicable also at high frequencies. Note, that at high switching speeds or frequencies, the dynamic (capacitive) component of the base current becomes much larger than the d.c./quasi-static component, so that its correct modeling is of higher importance for those applications.

The quasi-static internal base current, which represents injection across the bottom emitter area, is modelled in HICUM as

$$i_{jBEi} = I_{BEiS} \left[ \exp\left(\frac{v_{B'E'}}{m_{BEi}V_T}\right) - 1 \right] + I_{REiS} \left[ \exp\left(\frac{v_{B'E'}}{m_{REi}V_T}\right) - 1 \right]$$

(2.5.0-1)

The saturation currents  $I_{BEiS}$  and  $I_{REiS}$  as well as the non-ideality coefficients  $m_{BEi}$  and  $m_{REi}$  are model parameters. The first component in the above formula represents the current injected into the neutral emitter; a corresponding  $m_{BEi}$ >1 represents effects such as Auger recombination and the (very small) modulation of the width of the neutral emitter region. The second component represents the loss in the space charge region due to volume and surface recombination; the value of  $m_{REi}$  is usually in the range of 1.5 to 2 so that this component only plays a role at low injection. It is used to model the decrease of the current gain at low current densities.

Analogously, the quasi-static base current injected across the emitter periphery is given by

$$i_{jBEp} = I_{BEpS} \left[ \exp\left(\frac{v_{B^*E}}{m_{BEp}V_T}\right) - 1 \right] + I_{REpS} \left[ \exp\left(\frac{v_{B^*E}}{m_{REp}V_T}\right) - 1 \right].$$

(2.5.0-2)

The saturation currents  $I_{BEpS}$  and  $I_{REpS}$  as well as the non-ideality factors  $m_{BEp}$  and  $m_{REp}$  are model parameters.

Since the recombination at low forward bias is more pronounced at the emitter periphery compared to the bottom, its contribution ( $I_{REiS}$  ...) to the internal base current component may often be omitted in order to simplify the model and the parameter determination.

In hard-saturation or for inverse operation the current contributions across the base-collector junction become significant. The component of the internal BC junction is

$$i_{jBCi} = I_{BCiS} \left[ \exp\left(\frac{v_{B'C'}}{m_{BCi}V_T}\right) - 1 \right]$$

(2.5.0-3)

The component for the external BC junction reads correspondingly

$$i_{jBCx} = I_{BCxS} \left[ \exp\left(\frac{v_{B^*C}}{m_{BCx}V_T}\right) - 1 \right]$$

(2.5.0-4)

In many practical cases, both components can be combined into one,  $i_{jBC}$ , between B\* and C', without loss of accuracy (in, e.g., the output characteristics). This simplifies parameter extraction and reduces the number of model parameters.

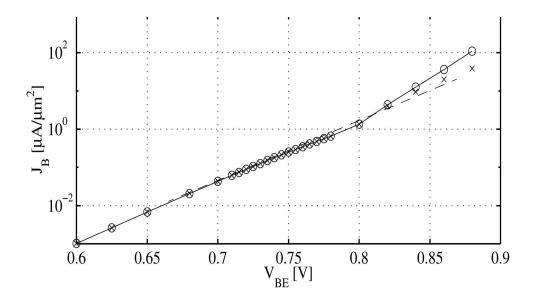

In various SiGe-HBT processes, an additional base current is observable that mostly results from the additional minority charge storage in the base at the barrier caused by the Ge drop within the BC junction [7]. The typical behavior is shown in Fig. 2.1.5/1 for the base current of a SiGe-DHBT. Triggered by the collapse of the electric field in the collector at high current densities, which can be described by the critical current  $I_{CK}$ , the conduction band barrier for electrons starts to form at about  $V_{BE} = 0.8$ V for the transistor under consideration. The resulting accumulation of electrons on the base side of the BC junction is compensated by an accumulation of holes, which leads to an excess recombination rate. As a consequence, the corresponding current can be approximated to a first order by

$$i_{Bhrec} = \frac{\Delta Q_{Bf}}{\tau_{Bhrec}} \tag{2.5.0-5}$$

with  $\Delta Q_{Bf}$  from (2.3.1-34) as the additional minority charge in the base, which increases rapidly above  $I_{CK}$ ; the corresponding recombination constant  $\tau_{Bhrec}$  is a model parameter. The current has been taken into account by adding a (controlled) current source in parallel to  $i_{iBEi}$ .

<u>Fig. 2.5.0/1:</u>Base current vs. base-emitter voltage for a SiGe-DHBT. Comparison between device simulation (circles), model without additional recombination component (dashed line) and model with additional recombination component (crosses).

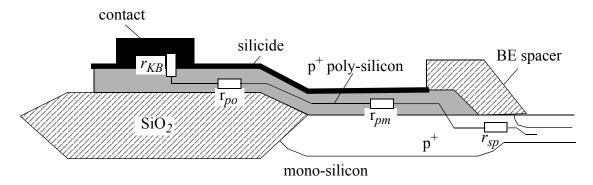

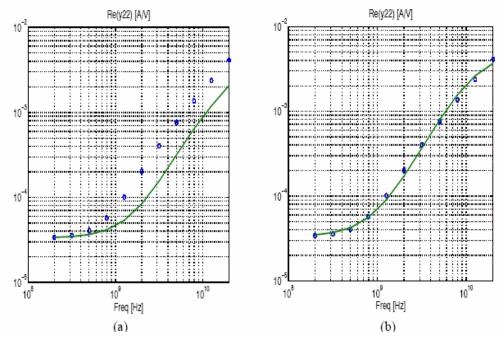

## 2.6 Internal base resistance

In HICUM, the internal and external base resistance are separately treated. The value of the internal base resistance  $r_{Bi}$  depends strongly on operating point, temperature, and mode of transistor operation (d.c., transient, h.f. small-signal). Especially the last mentioned dependence is a very complicated issue for high-speed large-signal switching processes.

The d.c. internal base resistance is modelled as

$$r_{Bi} = r_i \psi(\eta) \tag{2.6.0-6}$$

and is in HICUM/Level2 defined by the *effective* emitter dimensions  $b_E$  and  $l_E$ . Both the resistance  $r_i$  and the emitter current crowding function  $\psi(\eta)$  are bias and geometry dependent. The effect of conductivity modulation is being discussed first.

Conductivity modulation is described by the expression

$$r_i = r_{Bi0} \frac{Q_0}{Q_0 + \Delta Q_p} , \qquad (2.6.0-7)$$

with  $r_{Bi0}$  as zero-bias internal base resistance, and the bias dependent portion  $\Delta Q_p$  of the stored hole charge,

$$\Delta Q_p = Q_{jEi} + Q_{jCi} + Q_f + Q_r \approx Q_{jEi} + Q_{jCi} + Q_f,$$

(2.6.0-8)

$Q_r$  is generally very small and hence is being neglected.  $Q_0$  is a model parameter that is physically related and often is close to the zero-bias hole charge  $Q_{p0}$ . Therefore,  $Q_0$  is calculated from  $Q_{p0}$  as,

$$Q_0 = (1 + f_{DQr0})Q_{p0}$$

(2.6.0-9)

with the factor  $f_{dQr\theta}$  as model parameter.

Under extreme bias conditions (such as base "reach-through" with  $Q_{jEi}+Q_{jCi}$  approaching  $-Q_{p0}$ ) or with odd combination of model parameters, (2.6.0-7) can cause a numerical instability due to division by zero or a negative resistance value, which is not physical. This can be avoided by ensuring that the denominator remains larger than zero for all conditions. Defining the normalized charge  $q_r=1+\Delta Q_p/Q_0$ , (2.6.0-7) is rewritten as

$$r_i = r_{Bi0} \frac{1}{f(q_r)},\tag{2.6.0-10}$$

where the smoothing function

$$f(q_r) = \frac{q_r + \sqrt{q_r^2 + a_{qr}}}{2}$$

with  $a_{qr} = 0.01$ , (2.6.0-11)

reaches the value 0.05 if  $q_r$  approaches -1. In a real transistor, reverse depletion charges lower than  $-Q_{p0}$  (>  $-Q_0$ ) are not impossible but extremely unlikely. Although this case is not avoided in the model for the charges themselves, the corresponding instability in  $r_i$  is avoided.

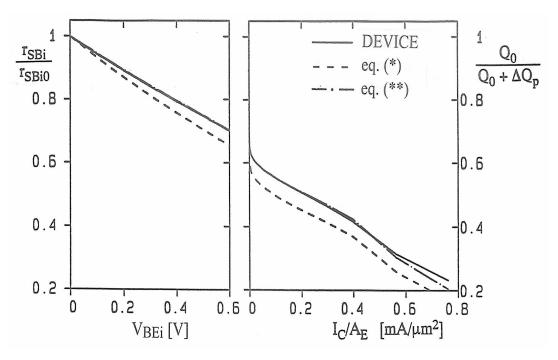

Fig. 2.6.0/1 shows the typical bias dependence of the (normalized) internal base sheet resistance due to conductivity modulation; the ratio  $r_{SBi}/r_{SBi0}$  is proportional to  $r_i/r_{Bi0}$ .

Fig. 2.6.0/1: Typical bias dependence of the normalized internal base sheet resistance and comparison to eq. (2.6.0-7) with  $f_{dQr0}$ =0 (labeled eq. (\*)) and  $f_{dQr0}$ >0 (labeled eq. (\*\*)) [27]. DEVICE corresponds to (1D) numerical device simulation; ( $V_{BEi} = V_{B'E'}$ ).

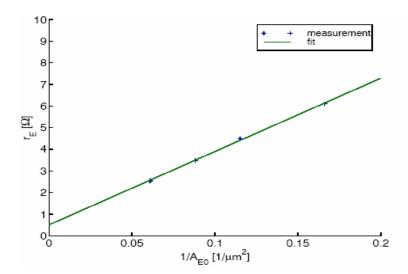

The zero-bias resistance  $r_{Bi0}$  is a model parameter which can be calculated (e.g., by TRADICA) as a function of emitter geometry and zero-bias internal base sheet resistance  $r_{SBi0}$ . For a transistor with  $n_E$  emitter contacts (or stripes) and arbitrary aspect ratio  $l_E/b_E \ge 1$ :

$$r_{Bi0} = r_{SBi0} \frac{b_E}{l_E n_E} g_i {2.6.0-12}$$

with the geometry function for  $n_E+1$  base contacts

$$g_i = \frac{1}{12} - \left(\frac{1}{12} - \frac{1}{28.6}\right) \frac{b_E}{l_E} . \tag{2.6.0-13}$$

The effect of emitter current crowding is described for all aspect ratios  $l_E/b_E \ge 1$  by the function

$$\Psi(\eta) = \frac{\ln(1+\eta)}{\eta} \tag{2.6.0-14}$$

with the current crowding factor

$$\eta = f_{geo} \frac{r_i i_{jBEi}}{V_T} \quad . \tag{2.6.0-15}$$

The factor  $f_{geo}$  is a model parameter which takes into account the geometry dependence of emitter current crowding (cf. Chapter 2.16). Hence, the final expression for the internal base resistance is

$$r_{Bi} = r_i \cdot \frac{\ln(1+\eta)}{\eta}$$

(2.6.0-16)

For transistors with narrow emitter contacts (or stripes) the influence of the charge storage at the emitter periphery on the dynamic transistor behaviour can significantly increase. In order to obtain acceptable computation times and to keep the extraction effort reasonable, the HICUM/LEVEL2 equivalent circuit does not contain a complete peripheral transistor element. Therefore, the peripheral charge has to be taken into account by modifying existing elements. The internal base impedance seen between the terminals B\*-E' is decreased by the (effective) peripheral charge  $Q_{fp}$  to

$$r_{Bi}^* = r_{Bi} \frac{\Delta Q_i}{\Delta Q_p} = r_{Bi} \frac{\Delta Q_i}{\Delta Q_i + Q_{fp}}$$

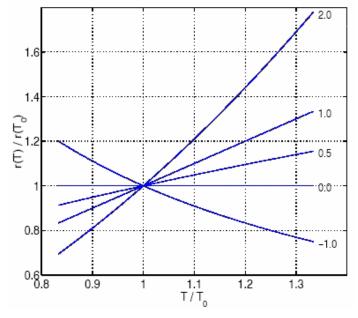

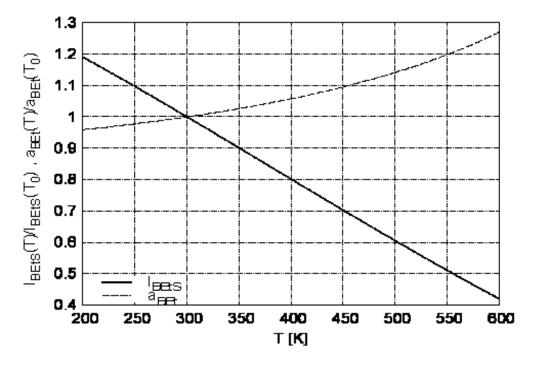

(2.6.0-17)